一种CAN总线转换USB接口的设计方案

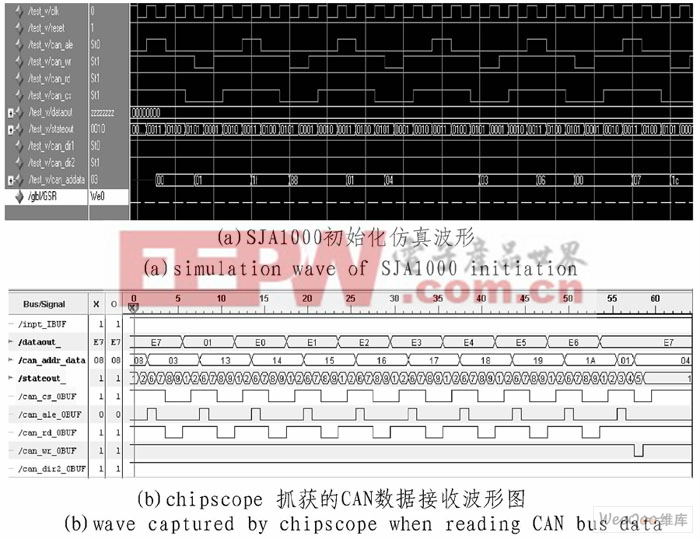

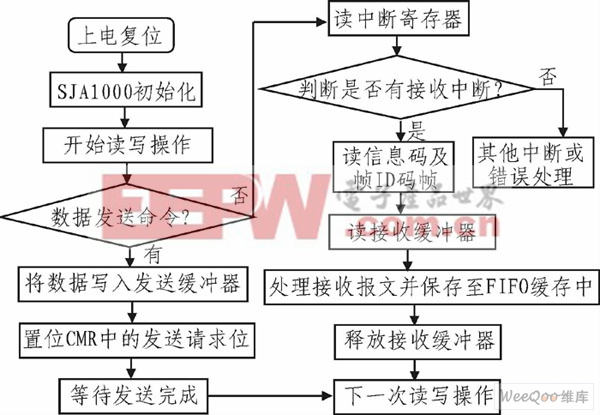

一段时间.等待SJA1000复位完成才能进行SJA1000初始化。初始化仿真波形如图5(a)所示。SJA1000内部有一个接收缓冲器和一个发送缓冲器。FPGA对SJA1000的读写操作,实际上对这两个缓冲器的读写控制。当FPGA接收CAN总线数据时首先读取SJA1000中断寄存器IR判断是否有接收中断。如果有接收中断到来则开始读取缓冲器内的8字节数据,然后释放接收缓冲器(写命令寄存器CMR)。使用Xilinx公司的Chipseope软件进行板上测试,测试数据为(E0,E1,……E7),抓取到的波形如图5(b)所示。FPGA读写SJA1000的流程控制图如图6所示。

图5 SJA1000逻辑控制波形图

图6 SJA1000读写控制程序流程图

2.3 CY7C68013A通信控制程序

CY7C68013A提供一种量子FIFO的处理架构,使USB接口和应用环境直接共享内部含有的4 K FIF0空间。本文CY7C68013A的控制是以异步SLAVE FIFO方式实现的,FPGA对CY7C68013A的逻辑控制实际上是对CY7C68013A内部FIFO的异步读写控制。设置CY7C68013A端点2为批量输入端点(FIF0地址为00),端点6为批量输出端点(FIF0地址为1O)。FPGA判断CY7C68013A的PA[1:0]端口电平,当PA[1:0]为01时,FPGA将接收到的CAN总线数据写入端点2对应的FIF0空间并上传给上位机,PA[1:0]为10时,FPGA读取端点6对应的FIFO内数据。FPGA对CY7C68013A的时序控制严格按照芯片手册完成。

由于USB数据包与CAN数据帧是基于两种不同协议的数据格式,因此在FPGA内开辟了2个512x8bit的FIFO缓存,并要进行必要的格式转换。例如,当从USB总线端注入的数据大于8字节时,需要将数据分成多帧传送给CAN总线;当数据小于8字节时则在数据后填充0。另外,在数据传送给CAN总线之前还需要添加适当的帧信息与帧识别码。

3 软件设计

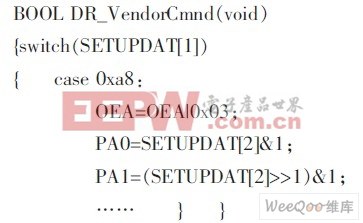

3.1 USB固件程序

USB固件程序是在Keil工具上开发完成的,除了进行必要的端点及寄存器配置外,程序中使用了自定义请求命令。自定义请求码通过USB控制传输的方式传送给固件,固件程序需要响应自定义请求码的请求信息。本文使用的自定义请求码为Oxa8,在响应代码中设置端口PA[1:0]电平值,产生USB控制命令,代码如下所示。SETUPDAT对应控制传输端点的Value值,由上位机应用程序设定。

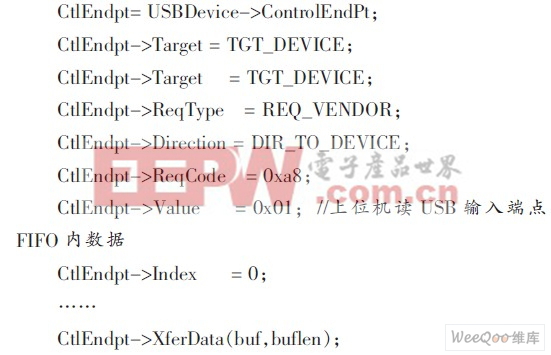

3.2 USB驱动程序及应用程序

使用Cypress公司提供的CY7C68013A通用驱动程序CyUSB.sys。上位机应用程序使用VC编写,也是基于Cypress提供的C++类库文件CyAP-I.lib设计完成的。使用的主要函数包括:BeginDataXfer、FinishDataXfer、XferData等函数。应用程序中设计了独立的数据接收线程,线程函数中不断地发送USB数据读命令,并完成批量输人端点的读操作。当有数据读入时,与主线程之间采用事件的线程同步方式,将数据读入计算机内存并保存。以下是线程函数中用于发送USB控制命令的控制传输代码:

4 实验调试与结果

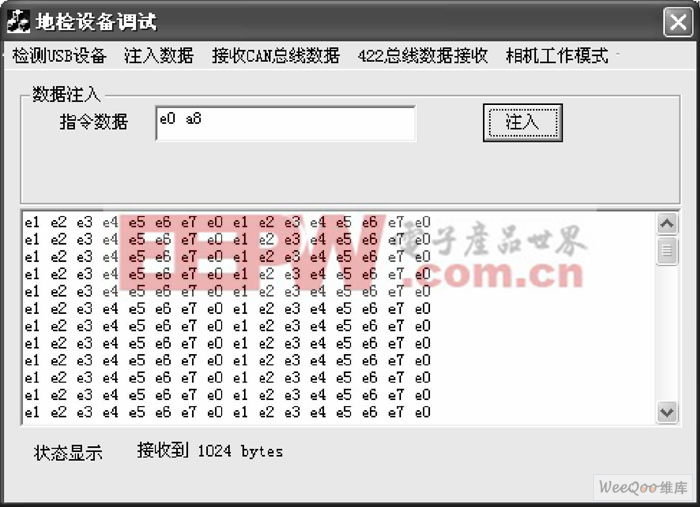

为验证设计的正确性,使用了周立功公司的USBCAN-I产品,与目标电路板组成双节点通信,2个节点设置相同波特率500 Kb/s(BTRO= 00,BTR1=1Ch)和相同帧格式,由测试软件ZLGCANTest发送一组数据(e0h,e1h,……,e7h),上位机应用程序接收到的数据如图7所示。反过来由上位机应用程序注入指令数据e0h,a8h,周立功软件接收到的数据为e0h,a8h,00h,00h……。经实验表明,数据收发正确,近距离通信时,通信速率可高达1 Mb/s。

图7 上位机应用程序图

5 结论

使用该方法设计的CAN总线转换器优点在于:使用USB总线完成CAN总线与计算机的数据交换,不会影响CAN总线的整体通信速率;通过FPGA控制完成通信接口的设计,可扩展性好,灵活性强,稳定性高。作为空间相机下位机地检设备的一部分,FPGA同时还可以完成RS422等总线的通信控制

接口 设计 方案 USB 转换 CAN 总线 一种 相关文章:

- μC/OS-II下通用驱动框架的设计与实现(07-23)

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)

- DSP和Flash接口技术的实现(08-15)

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)