MSP430x4xx系列微控制器的独特时钟设计

来控制其分频比FLL div,以对ACLK进行1、2、4、8等分频。分频后的输出可以用来为外围电路提供时钟。

3 FLL+的工作原理

对于RC振荡器,由于其频率会随温度和电压的变化而变化,因此在对时钟精度要求较高的情况下,DCOCLK通常要通过FLL进行校频后,才能用于系统时钟。

3.1倍频方案

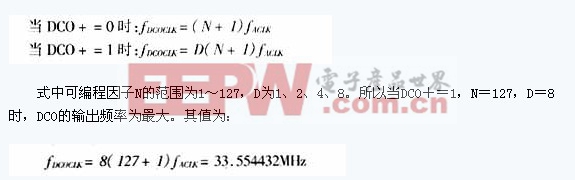

在需要较高数据处理速度时,ACLK就不能单独胜任,在这种情况下,就要用到倍频技术。为了支持更大范围的频率变化,FLL+的倍频方案增加了DCO+控制位。当DCO+取0、1时,fDCOCLK输出时钟频率不同,具体如下:

式中,fACLK取32768Hz。可见,通过改变N、D和DCO+,可以很容易地调节用作MCLK/SMCLK的DCO频率。但要注意,最后得到的MCLK不能超过器件的工作频率。

3.2频率抽头

DCO的输出时钟为DCOCLK,这个时钟被(D×(N+1))分频后应与ACLK进行比较。若DCOCLK用于系统时钟MCLK,则同步器将对 ACLK和MCLK/(D×(N+1))进行比较,然后用比较所得的差值来对一个10位的频综器进行“up”或者“down”模式计数。这样, MCLK/SMCLK就可以在1024种可能的设置上不断地进行调节。一旦频率被锁定,同步器输出的误差信号就变为0,此时有MCLK=N×ACLK。在频综器的10位输出中,5位用于DCO频率抽头(NDCO),另外的5位用于频率调整(NDCOMOD)。5个抽头可组成29种频率(28,29,30和31抽头是一样的),每一个抽头比前一个要高约10%。

明显可以看到:DCO只能产生一些离散的频率分量。所以说仅仅依靠改变N、D和DCO+无法使同步器的输出达到严格的0。

3.3频率调整

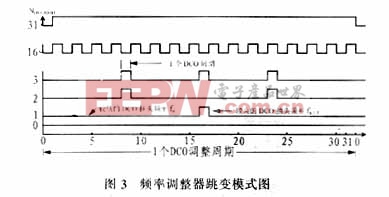

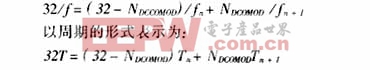

DCO频率调整器的作用是通过混合相邻的DCO周期来减小长期的累计周期变化。换句话说,就是通过控制fn+1在一个调整周期内所占的比率来减小输出频率与所需频率之间的误差。具体的频率调整器跳变模式如图3所示。图中,调整器以32个DCO时钟周期为一个周期。NDCOMOD可用于定义需要混合的fn+1的比例常数。

下面的公式定义了DCO长期输出频率与相邻跳变频率之间的关系:

由此可见,频率调整器通过为每个DCO周期独立地选择fn或者fn+1,来调整DCO的输出频率,进而实现分数抽头的目的。

必须明确的是,MCLK的精度只是建立在平均的基础上。对于短期精度,由于每个周期来自相邻的DCO频率抽头,因此是不精确的;而对于长期精度,由于经过了累加平均,因而相对误差被减小了。实际上,由于调整器的周期为32,每次调整量为每一频率段的10%,因此相对误差可降到低于0.33%。

也可以通过软件编程NDCOMOD来确定DCO的输出频率,以便用FLL锁频时达到快速锁定的目的;而在不用FLL时,可不用外部晶振来产生所需频率。假如所需频率f为100Hz,并假定DCO在0抽头时的频率为f0=700Hz。则与f相邻的两个频率为:

将这两个频率代入上面的公式中,便可以求得NDCOOD=24。所以,若DCO中心频率为1MHz,那么,将24写入与NDCOMOD相应的寄存器中,即可在无外接晶振的条件下获得所需时钟。在这种应用条件下,需要注意几点:

●FLL和调整器在系统复位时默认为允许,要工作在这种状态,必须首先禁止FLL。否则DCO会自动锁定到f0;

●f0是不确定的,在具体应用时应先测定,然后再用它来计算所需的相邻频率。

●由于DCO的输出频率会随着稳定度和电压的变化而漂移,所以不能应用于对时钟精度要求较高的场合。

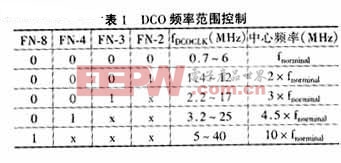

3.4 DCO频率范围控制

在通过调节倍频因子N改变MCLK时,FLL+调节DCO的频率将趋于目标频率。当MCLK稳定在新的频率抽头之前,每向下一个DCO抽头,其变化一次需要1024个时钟周期的延时。可以看到,对于MCLK的大范围频率变化,将需要很大的时延才能达到稳定。对此,MSP430x4xx系列采用了一种频率分段的机制来处理这种大范围的频率变化。即将DCO输出的700kHz~40MHz分为5段,每一段的中心频率基于典型频率fnominal(2MHz)的倍数。使用时可以通过控制寄存器SCFI0的FN_8、FN_4、FN_3、FN_2等四位对它进行控制。表1列出了DCO的频率范围控制方法。由表中可见,通过控制这些位可在不改变当前抽头设置的情况下改变DCO的输出频率MCLK(实际上是立即选择了相邻的抽头,而不是逐个调节)。因此,在这种方式下,DCO调节到所需频率的时间比仅仅通过调节倍频因子要短得多。所以首先应根据所需频率来调整DCO的中心频率,或者在MCLK变化较大时及时调节 DCO的中心频率。

4用FLL+优化系统性能

MSP430x4xx正是由于采用了上述FLL+时钟模块,才使它的全局性能得到了优化。同时,它还提供有灵活的时钟配置选择,各个模块的时钟都可用软件选择。也可以根据系统的具体要求来动态调

时钟 设计 独特 控制器 系列 MSP430x4xx 相关文章:

- 嵌入式同步时钟系统的设计与实现详解(05-19)

- 用DSP实现抖动(Jitter)测量的方法(04-28)

- Linux 时钟管理(06-13)

- VxWorks for x86系统中实时时钟的应用(07-06)

- μC/OSII的时钟中断技术研究(06-30)

- 一种嵌入式时钟管理器的设计与实现(08-01)