一种嵌入式的实时视频采集系统设计

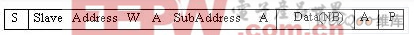

以是读或写两种方式,其写格式为:

其中:S为总线起始信号;Slave Address W为被控器SAA7111的寻址字节;A为被控器应答信号;SubAddres为SAA7111控制寄存器的地址;Data(NB)即控制寄存器的配置参数;P为总线终止信号[3]。

3.3 FPGA的采集控制原理

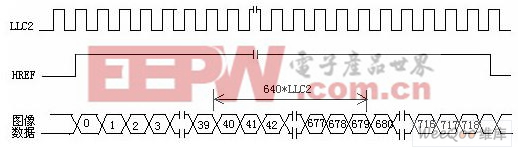

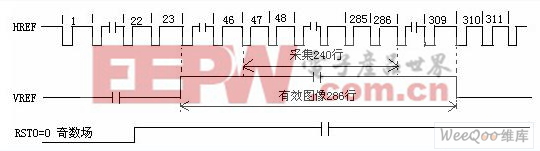

SAA7111A的输出时钟信号包括LLC(27MHz)和LLC2(13.5MHz),其中LLC2为像素时钟频率,每一时钟对应一个16位像素输出。行参考同步信号HREF,高电平表示一行的有效像素,为720个LLC2周期。场参考同步信号VREF高电平时表示输出是有效行图像,单场是286行;低电平期间为场消隐信号,是26个行周期。RTSO=1时表示输出为奇数场,RTSO=0时为偶数场[4]。输入信号FEI为输出使能信号,为0时允许数据输出,为1时数据输出处于高阻状态。图4,5分别为采集一行和奇数场图像的信号时序图。

图4 SAA7111A采集一行图像的时序图

启动采集前必须对SAA7111A内部的32个寄存器写入相应的值。在采集的过程中,仅采集奇场图像信号而不采集偶场图像信号。因为只采集奇场信号也能得到稳定的图像,而可以利用偶场图像时间等待处理图像。对有效像素、无效像素、有效行和无效行进行计数,产生RAM的地址、读写、选通等控制信号,均由FPGA完成。由于只采奇场图像,行数也减少为原来的一半,为286行,前后各去掉23行,取中间240行。当RTSO为高电平且VREF上升沿到来时,标志奇数场开始,启动无效行计数器对HREF信号进行计数,计满前23行后,启动有效行计数器,置COUT信号为高电平,且在水平同步信号VREF=1、垂直同步信号HREF=1、

图5 SAA7111A奇数场采集的时序图

奇偶场信号RTSO=1时,启动无效像素计数器,对LLC2二分频后的像素时钟信号进行计数。LLC2二分频后频率降为6.75MHz,每行像素点由原来的720点,减少为360点,将其截头去尾,前后各去掉20个像素,取一行中间的320个像素点,即得到分辨率为320 X 240的一帧图像[5]。当无效像素计数器计满前20后,启动有效像素计数器开始计数,并将数据缓冲器打开,每计一次数,地址发生器加1,产生地址信号,读写信号WR,选通信号RAM_SEL,当一帧图像写完后,置FLAG信号为低,触发中断信号,以便处理器处理图像。值得注意的是,利用FPGA可以很灵活地控制存入RAM存储器中的图像数据量。这里将图像分辨率设计为320 X 240,实际应用中,可以根据需要灵活设置。

4 结束语

本文作者创新点:该系统能够完成对视频信号的采集,适应性极强的FPGA主要用于控制图像信号的采集,FPGA除了完成对SAA7111A配置以外,还完成图像提取处理、图像存储地址产生器等功能。由于FPGA的在线可编程特性使该系统变得更加灵活。此外,成熟的编译环境和FPGA与SAA7111A简单的外围电路大大缩短了开发和调试的周期。在未来的FPGA中还可以加入图像预处理流程,缩短后续处理时间,因此具有较高的推广价值。实验表明,系统速度快、可靠性高、实时性好,在视频采集和图像处理方面有着很好的应用前景。

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)