嵌入式系统中存储器性能研究

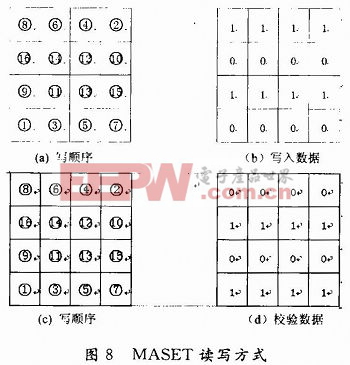

3.3 MASEST

MASEST读写方式的检测对象也是地址译码器。不过侧重于地址译码器的翻转噪声。按照图8中的顺序写入行带状数据,此顺序的目的是让地址译码器译码每次输出都尽可能多的翻转。然后在按此顺序校验,校验同时把数据翻转。最后顺序读取数据校验。

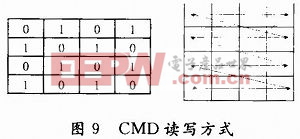

3.4 CMD

CMD读写方式检测内存单元间的相互干涉。如图9,首先写入棋盘数据。然后按照如图9顺序校验。

3.5 ROW/COL组合

ROW/COL组合测试的对象是内存控制电路。内存单元阵列分为行和列,某一个行地址有效时,对某一个单元进行读/写组合的操作,由于内存单元需要定时刷新,这种操作可能对刷新造成影响。ROW/COL组合读取方式固定某一行,对一个单元进行读/写组合操作,验证刷新的影响。然后对同一行的下一列进行相同的操作。

4 测试系统

上面讨论了用于测试内存的数据和读取方式。在实际组成的系统中,针对特定的测试对象,两者总是结合使用的。下面的表1列出了本测试系统测试的项目和相对应使用的数据和读取方式。

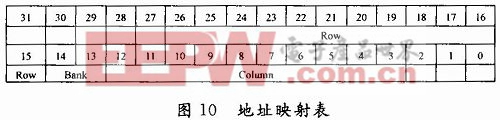

前节讨论的数据和读取方式的时候,都是基于动态内存的实际结构,从内存单元矩阵行地址,列地址来分析的。实际应用过程中,内存控制器总是把内存单元矩阵映射成线性连续空间的。不同的芯片组会给出不同的映射方法。图10是Intel BX 440芯片组的内存行列地址映射(128 MB)。本测试系统测试的时候需要了解硬件的结构,才能有效的找出内存潜在的缺陷。

测试系统基于嵌入式Linux操作系统,采用命令行方式运行,所有的输入采用配置文件来设定。下面给出了一个配置文件的例子:

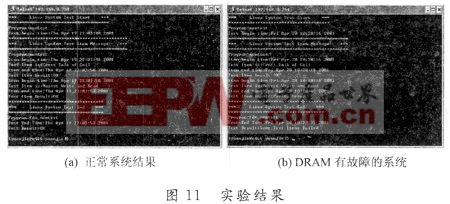

在正常和DRAM系统有故障的嵌入式系统下面分别得到了如图11的检测结果,从实验中可以发现有故障的系统在测试过程中某些测试项目无法通过,根据具体的情况就可以大致判断出故障的原因,这样就给系统设计者指明了改善系统性能的方向。

5 结语

本文研究从动态内存的失效模型出发,针对不同的部件可能发生的问题,设计了检测用的数据和读取方式,将它们组合起来进行测试,可以更有效地检测动态内存中潜在的缺陷,具有高的失效类型的覆盖率。同时,动态内存测试作为嵌入式Linux测试系统的一个子系统得到了国际计算机系统制造商富士通公司的认可。

- 基于DSP的音频会议信号合成算法研究(05-10)

- 基于定点DSP的MP3间频编码算法研究(07-04)

- DSP的并联电力有源滤波器的仿真研究(02-15)

- PCI总线数据采集系统的硬件研究(09-12)

- PIC单片机在温度测量领域的应用及仿真研究(11-23)

- 嵌入式软PLC 的设计与研究(06-27)