ARM9高速实时多任务数据采集系统的算法优化

在处理完命令扫描和采样任务之后,影响整个系统性能的就剩下上位机和下位机显示部分了。显示任务工作原理如图4所示,利用μC/OSII系统提供的消息队列对显示部分进行改善。分别建立两个长度为16的消息队列和内存块链表,数据提交任务从空闲内存池中得到可用内存块之后将本任务要显示的数据存入该内存块,此时该内存就变成了带有数据的待显示数据块。而后将该内存块的地址以消息的形式注册在显示消息队列上。消息队列的长度设置为16,虽然这里只有12个任务会发送消息给消息队列,但在实时多任务程序中,各个任务的运行是随机的,消息队列在一段时间内得到的消息个数是个不定值,所以留出4个空位作为裕度。而且设置初始值为16的计数信号量来保护消息队列,数据提交任务在提交数据之前先检测该信号量,如该信号量有效就可以发送信号,如信号量无效则需等待,直到有可用信号位时方可将信号发出。在外部硬件操作端,由外部发送任务将消息队列中的消息按照固定速率发送到外部信号线上。

这样设计,消息队列就相当于一个缓冲区,使得所有提交任务都可以向这个缓冲区发送待显示数据,有效地避免了多个任务争用一个外围设备而引起的死锁、竞争冒险等问题。同时减少了任务数量,减少了任务切换的次数,充分利用了系统时间,提高了系统性能。

3.4 关键区保护

多任务设计中每个任务在任何时刻都可能被其他任务打断,必须充分考虑代码的安全性、可重入性、可靠性、饥饿、互锁、死锁等情况。[3]

为了避免上述情况,任务间消息发送和传递时以及在数据采样时对相应函数体进行关键区保护,在这些函数运行的时候禁止中断和任务调度,以保证数据传递和数据采样的绝对正确性和系统运行的绝对安全性。

4 极限频率测定及总结

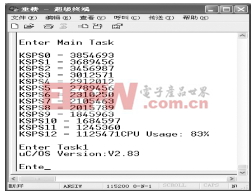

上位机超级终端接收到的极限频率测试结果如图5所示。

图5 极限频率测量结果

分别测试了高频段、中频段和低频段的极限频率,结果在CPU使用率80%~90%的情况下测定。该系统成功实现了智能化设计和优先级动态调度、系统参数动态设置等功能,达到了设计指标。

参考文献

[1] Labrosse Jean J.嵌入式实时操作系统μC/OSII [M].邵贝贝,等译.北京航空航天大学出版社,2007.

[2] Love Robert.Linux内核设计与实现[M].陈莉君,等译.北京:机械工业出版社,2010.

[3] Labrosse Jean J.μC/OSIII—The RealTime Kernel,200909.

系统 算法 优化 数据采集 任务 高速 实时 ARM9 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)