基于CPLD非多路复用/多路总线转换桥设计/实现

1 多路复用总线的信号和时序

1.1 SJA1000SJA1000接口的主要信号说明

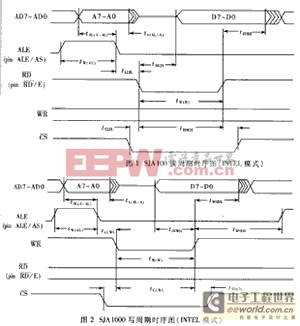

CAN控制器SJA1000提供的微处理器接口方式为典型INTEL或MOTOROLA地址数据多路复用总线模式,主要信号有地址数据信号AD7~AD0、地址选通信号ALE、片选信号CS、读信号RD、写信号WR、模式选择信号MODE。当MODE=1时,为INTEL模式;当MODE=0时,为MOTOROLA模式。本文描述的地址数据多路复用总线模式均为INTEL模式。图1和图2分别为INTEL模式读、写周期时序。AD7~AD0引脚在ALE有效时,传送的是地址信号;在RD或WR有效时,传输的是数据信号。

|

1.2 SJA1000SJA1000的时序分析

以SJA1000的读时序为例进行说明。在设计转换桥时,多路复用总线的各信号必须满足如下时间参数要求:ALE的脉冲宽度(tW(AL))最小为8ns;地址信号(A0~A7)建立到ALE变为低电平所需时间(tsu(A-AL))最小为8ns;RD的有效脉宽(tW(R))最小为40ns;RD为低电平到数据信号(D7~D0)有效所需时间(tRLOV)最大为50ns;RD变为高电平到地址数据线释放(即高阻状态)所需时间(tRHDZ)最大为30ns。

2 非多路复用总线的信号和时序

2.1 TMS320F206接口的主要信号说明

TMS320F206的总线接口方式采用地址和数据分离的形式。其主要信号有地址信号A0~A15、数据信号D0~D15、读信号RE、写信号WE、闸门信号STRB、I/O空间选择信号IS、数据存储器选择信号DS、程序存储器选择信号PS、机器时钟输出信号CLKOUT1。当对外部数据存储器、程序存储器或I/O空间访问时,STRB有效;当对外部I/O访问时(即程序中使用PORTR和PORTW指令),IS有效。

2.2 TSM320F206的I/O时序分析

TMS320F206的读写时序如图3和图4所示。I/O的读或写工作周期一般在两个机器周期内完成。在此期间,IS信号和地址信号一直保持有效;闸门信号STRB发生在第一个机器周期有效后并保持一个机器周期以上;RE和WE有效时,数据有效。两次连续的写操作(如图4所示)时,WE的有效间隔时间tW(WH)最小为(2H-4)ns,而两次连续的读操作(如图3所示)时,RE的有效间隔时间tW(RDH)为(H-4)ns~Hns,其中H为0.5倍的机器时钟周期。可见对于连续的读、写操作,RE、WE的有效间隔不同,设计电路时应注意此细节。在连续的读或写操作时,IS信号一直为有效电平'0',无法以此信号作为产生SJA1000的ALE、读、写信号起始基准;而在写周期时,STRB与WE的变化始终保持一致,因此在产生SJA1000写周期时,可以用STRB作为ALE、WR产生的起始基准信号。但是TSM320F206

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)