FPGA实现多处理器解决方案

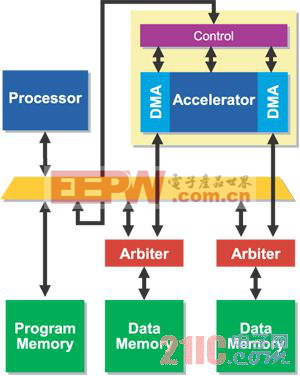

要求。 基于FPGA的嵌入式系统提供灵活的性能,支持最后一刻更改,根据客户要求来提升系统性能。将 含有大量计算的算法转换为FPGA中的逻辑后,其运行速度比微处理器或数字信号处理器实现的相同软件算法快出几个数量级。更重要的是,硬件资源可提供给对性能要求高的算法,从而降低了对高性能CPU的需求,并降低了时钟频率和功耗,简化了电路板设计。 扩展指令集 多个处理器IP供应商能够扩展处理器指令集,以包含在硬件中实施的专用算法,并在FPGA中实现。采用处理器常用的加载/存储操作,数据可馈入到定制逻辑模块中,成为处理器算法逻辑单元(ALU)的一部分。在有些情况下,定制指令能够支持多周期操作,实现对FIFO和存储器缓冲等其他系统资源的访问。定制指令的典型应用包括位处理、复杂的数值和逻辑运算等。 依靠处理器加载和存储操作,定制指令与采用通用ALU资源运行同样算法相比,具有明显的性能优势。例如,64kbyte的循环冗余校验(CRC)以定制指令运行时,运行速度比软件快出27倍1。不同的应用具有不同的性能结果,但是总体上比单独采用软件快得多。 处理器IP供应商不同,开发人员如何使用定制指令也各不相同。例如,在加入定制指令时,有的必须生成一个新的编译器。然后,根据应用标准,这种定制编译器导出定制指令调用。更简单的方法是由用户在其C源代码中作为子程序来直接调用指令。由于软件设计人员能够更清楚的掌握何时使用定制指令,因此这种方法更自然一些。 提升系统性能的多种方法 其他提升系统整体性能的方法包括利用硬件加速(也称为协处理器)、处理器协同芯片以及定制片内系统等。 与定制指令不同,硬件加速器作为独立的逻辑模块直接从嵌入式CPU获取指令,不需要CPU干预,处理全部数据缓冲。一个简单的模块框图包括带有两个1/2 DMA通道的处理模块(一个读取输入数据,另一个存储结果)以及一个控制接口,用于CPU建立、启动、停止以及工作中对各单元的轮询等。这种体系结构非常适合于对大块数据的处理,此时,CPU加载数据并存储结果成为性能瓶颈。 硬件加速器由于其固有的自治特性,能够比软件运行任务提高几个数量级的性能增益,因此加速功能通常在硬件中设计实现。 不管CPU是否在FPGA内部,与FPGA连接的分立处理器和DSP协同芯片都可以使用硬件加速、扩展外设以及接口桥接等。现在,可直接使用芯片间接口IP,实现对FPGA内部外设、加速逻辑和I/O接口的外部访问。 总结 在FPGA中采用多个软核处理器,根据时间和功耗要求划分任务,可高效使用处理能力,与分立处理器相比,具有相同甚至更高的整体性能。多个软核处理器还可以用作分而治之的策略,来提升系统整体性能或者卸载现有处理器任务,这种策略仅受目标FPGA逻辑和存储器资源的限制。 一类新的硬件开发工具、知识产权内核以及FPGA体系实现了这些技术的主流应用。在嵌入式领域,由于这些技术的成功,主要FPGA供应商进一步加大了开发和投入。在您下一个设计中,应考虑如何应用这些技术。

- SN2005学习系统 数字语音室解决方案(05-19)

- 以可编程DSP架构应对TD-SCDMA以及TD-LTE带来的设计挑战 (02-14)

- 基于DSP的电源解决方案(06-13)

- FPGA PCIe 视频采集(Video Capture)解决方案分析(06-06)

- 大联大友尚集团推出基于Realtek的智能插座解决方案(10-22)

- Wind River携手Cavium推出新的多核软件解决方案(09-12)