用单片机实现可编程逻辑器件的配置

程逻辑器件

用单片机配置可编程逻辑器件与上述PS配置方式原理一致,只需模拟PS配置方式中DATA0、DCLK、nCONFIG、CONF_DONE、nSTATUS引脚的配置时序,将配置数据串行移入PLD。配置引脚的功能如表1所示。

3.1 硬件设计

用单片机配置PLD,可以使用普通输入输出口或单行口。使用普通I/O口(如P1口),向PLD发送1Bit数据至少需要4个指令周期。一个指令给DATA0赋值,两个指令产生DCLK时钟,一个指令移位取数据。如果晶振为fosc,一个指令周期为12/fosc,因此它的下载速率为fosc/48。然而如果采用串行口方式0,其下载速率提高为fosc/12。考虑到PLD配置文件数据比较大,通常都在数十千字节以上(其配置文件大小如表2),为了加快配置速度,并适合各种不同规模的PLD,采用了WINBOND78E58单片机。

该单片机外接晶振最大频率为40MHz,它在串行口方式0下波特率可设置为fosc/4。另外通过设置特殊功能寄存器CKCON的MD0、MD1、MD2三位,可以将MOVX、MOVC等指令周期缩短至2个机器周期。与普通单片机相比,可使配置时间大为缩短。WINBOND78E58单片机内部拥有32KB FLASH ROM.由配置文件数据表2可知,只需一片单片机就可以对EPF10K20系列以下的PLD进行配置了。本系统中使用了一片APEX20K300E,因此在硬件电路设计中,扩展了一片WINBOND29C040 FLASH存储器(容量为512KB),其电路如图2。DATA0与RXD、DCLK与TXD、nCONF与P15、CONFIG_DONE与P16、nSTATUS与P17分别相连。

3.2 软件设计

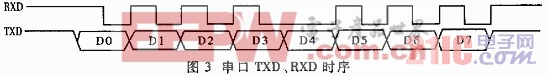

在软件编程时,使用了串行口移位寄存器输入输出方式。本系统只需用到输出方式,串行数据通过RXD引脚输出,而在TXD引脚输出移位时钟。当一字节数据写入串行数据缓冲器SBUF时,就开始发送。在此期间,发送控制器送出移位信号,使发送移位寄存器的内容右移一位,直至最高位(D7位)数字移出后,停止发送数据和移位时钟脉冲。RXD、TXD时序如图3。由图3可知,它可以用来模拟配置时序。发送完一字节数据后,硬件置发送标志位TI为1,向CPU申请中断。若CPU响应中断,则从0023H单元开始执行串行中断服务程序。

为了提高配置速度,单片机程序用汇编语言编写。单片机上电后使nCONFIG脚由低到高复位待配置PLD;当判断到nSTATUS为高后,开始从外部FLASH存储器取数据串行移位。配置过程中,查询CONF_DONE。一旦为高,配置完成,但还要送40个DCLK脉冲,PLD才能进入用户工作状态。

用户设计PLD程序经MAXPLUS II或QUARTUS编译后将产生后缀后为.sof的SRAM目标文件。该文件含有除配置数据以外的控制字符,不能直接写入到PLD中去,需要利用软件的编程文件转换功能将文件转换成.rbf(Raw Binary File)十六进制文件。把.rbf文件烧写到存储器中,单片机通过MOVX指令读入后,串行移位到PLD。

部分asm语言源程序如下:

NCONFIG BIT P1.5

CONFDONE BIT P.6

NSTATUS BIT P1.7

ORG 000h

……

CLR SM0

CLR SM1 ;SM0,SM1为0,串口工作于方式0

CLR SM2 ;串口波特率为fosc/4

CLR REN

ANL 8EH,#0f8h ;地址8EH是CKCON单元,MD0、MD1、MD2清0

CLR EA

WJRESTART:CLR NCONFIG

SETB NCONFIG ;上升沿复位PLD

WAIT:JNB NSTATUS,WAIT ;NSTATUS为高,可进行配置

WJPEIZHI:MOV P1,COUNTER3

MOV DPH,COUNTER2

MOV DPL,COUNTER1 ;配置数据大,需3个单元作地址记数

MOVX A,@DPTA

MOV SBUF,A ;串行移位

NOP

NOP ;采用填充2个空指令,正好使一个字节发送完成,可发送下一个字节

INC COUNTER1 ;地址加

MOV A,COUNTER1

JB CONFDONE,WJEND1

CJNE A,#0,WJPEIZHI

INC COUNTER2

NOV A,COUNTER2

CJNE A,#0,WJPEIZHI

INC COUNTER3

LJMP WJPEIZHI

WJEND1:MOV R0,#60

WJEND:WOV A,#55H

……

MOV SBUF,A ;由此产生40个DCLK时钟

DJNZ R0,WJEND

WERE:LJMP HERE ;配置完成,进入用户工作模式

使用OTP(One Time Programming)器件配置CPLD具有一定的冒险性,一次简单的代码更换就可能意味着更换OTP器件,并重新开始所有的程序。被动串行微处理器(Passive Serial With Processor)配置方式以EEPROM为基础,允许对这些存储器进行多次编程,所有其它芯片都无需从已装配的印制电路板上拆卸下来。高速读写周期的FLASH存储器能确保1万次编程,而且能对任何以SRAM为基础的PLD下载。该方式除了在加电期间能承载配置数据外,还有许多方便之处。例如,用户可以将多个配置文件.rbf分区编程到外部存储器的未用区段,通过单片机读取不同存储区可以将可编程逻辑器件在线配置成多种不同的工作模式。

- 基于TS201的多DSP系统设计与实现(04-17)

- 基于Zynq的OLED驱动设计(10-04)

- 可编程逻辑器件设计技巧(06-06)

- CPLD/FPGA技术及电子设计自动化(06-06)

- FPGA管脚分配需要考虑的因素(06-06)

- 分时复用时CPLD设计变频系统中的应用(06-06)