基于单片机的现场可编程门阵列的配置

1 引言

在大规模可编程逻辑器件出现以前,把器件焊接在电路板上是设计数字系统的最后一步。当设计存在问题并解决后,设计者往往不得不重新设计印制电路板。设计周期长,设计效率低。CPLD 、FPGA出现后,利用其在系统可编程或可重配置功能,设计者可以在进行逻辑设计而未进行电路设计时就把CPLD、FPGA焊接在电路板上,然后在设计调试时可一次次随心所欲的改变电路的硬件逻辑关系,而不用改变电路板的结构。

2基于SRAM的FPGA的结构和原理

可编程逻辑器件从结构上可分为:

⑴ 乘积项结构器件。其基本结构是与-或阵列的器件,大部分简单PLD和CPLD多是这种器件。

⑵ 查找表结构器件。由简单的查找表组成可编程门,再构成阵列形式。大部分FPGA

器件都采用基于SRAM的查找表结构。如XILINX的XC4000系列pSPATRAN系列,ALTERA的FLEX10K 系列pACEX系列都是基于SRAM查找表的典型FPGA器件。查找表(LUT)是一种函数发生器,一个N输入查找表能实现N个输入变量的任何逻辑功能。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成有4位地址线的16×1bit的RAM。当用户通过GDF原理图或VHDL语言描述了一个逻辑电路后,FPGA开发软件会自动计算逻辑电路的所有可能结果,并把结果事先存入查找表。这样,当多个信号进行逻辑运算时就等于输入一个地址进行查表,找出地址所对应的内容,然后将其输出即可。

3 FPGA的配置原理

FPGA使用SRAM单元来保存配置数据。这些配置数据决定了FPGA内部的互连关系和逻辑功能,改变这些数据,也就改变了器件的逻辑功能。由于SRAM 的数据是易失的,因此这些数据必须保存在FPGA器件以外的EPROM、EEPROM或FLASH ROM等非易失存储器内,以便使系统在适当的时候将其下载到FPGA的SRAM单元中,从而实现在系统可重配置ICR(In-Circuit Reconfigurability)。ALTERA公司的FPGA有两种配置下载方式:主动方式(AS)与被动方式(PS)。在实验系统中,通常用计算机或控制器进行调试,可采用被动方式。将在FPGA集成开发环境(如QUARTUSII)下经编译p仿真后形成的编程文件用下载电缆下载到FPGA中,进行硬件调试与验证。电路设计成功后,将配置数据烧写固化在一个由ALTERA生产的专用EEPROM(如EPC1441)中。上电时,由这片配置 EEPROM先对FPAG加载数据,几十毫秒后,FPGA即可正常工作。

ALTERA的FPGA有六种配置模式:配置器件pPS(Passive Serial)模式pPPS(Passive

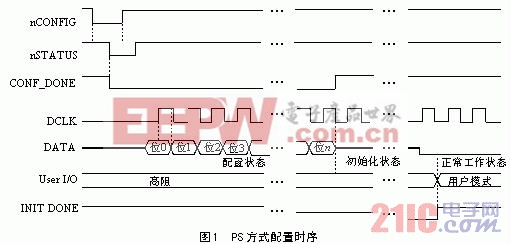

Parallel Synchronous)模式pPPA(Passive Parallel Asynchronous)模式、PSA(Passive Serial Asynchronous)模式pJTAG(Joint Test Action Group)模式。其中,PS模式因FPGA与配置电路的互连最简单,对配置时钟的最小频率没有限制而应用最广泛,因此在ICR控制电路中通常采用PS配置方式来实现ICR功能。FPGA器件有三种工作状态:配置状态,初始化状态,正常工作状态(用户模式)。其时序如图

4 用单片机配置FPGA

目前很多产品都广泛用了FPGA,虽然品种不同,但编程方式几乎都一样:利用专用EPROM对FPGA进行配置。专用的EPROM价格不便宜,且大都是一次性OPT方式编程。一旦更改FPGA设计,代价不小。而且在FPGA实际应用中,设计的保密性和可升级性是非常重要的,用单片机来配置FPGA可以很好的解决上述问题。单片机用PS模式配置FPGA的时序与图1相同。配置时关键是用单片机产生合适的时序。

4.1 硬件设计

FPGA的配置文件比较大,通常在数十千字节以上。本系统对ALTERA公司的EPF10K20进行配置,其配置文件大小为29KB,因此可采用一片 89C51单片机,外扩展一片27256存储器,存放FPGA配置数据。单片机与FPGA间数据传输采用串行口,电路如图2。单片机上电后,根据系统要求,利用P1.1、 P1.2、 P1.3、 RXD、TXD5个I/O口将存储在27256中的配置数据下载到电路中的FPGA器件中。

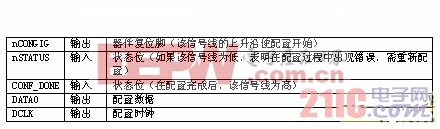

表1 配置引脚功能说明

4.2 软件设计

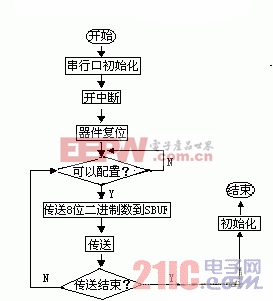

在软件编程时,采用串行口工作方式0:移位寄存器方式。本程序以方式0发送,发送数据从RXD引脚输出,TXD引脚输出同步移位脉冲。当一个字节数据写入发送数据缓冲器SBUF时,启动串行发送。每发送一位二进制数,寄存器右移一位,直到八位二进制数发送结束,置发送中断标志TI。CPU响应中断,执行中断服务程序。重复测试CONFIG_DOWN,直到CONGIG_DOWN为高电平配置结束。此后在经初始化,FPGA才能进入用户工作状态。

图3 主程序流程图

参考文献:

[1] 胡乾斌,李光斌,李玲等。 单片微型计算机原理与应用.武汉:华中科技大学出版社,2002

[2] 潘松,黄继业。EDA技术实用教程.北京:科学出版社,2004

[3] 刘晓明。王军,谢明钦。基于单片机的复杂可编程逻辑器件快速配置方法.电子技术应用

- DSP在LED显示中的应用(08-21)

- 基于DSP+DUC的短波阵列信号发生器设计(05-27)

- 麦克风阵列信号采集系统的设计(10-25)

- 基于FPGA的活套高度和张力系统解耦控制器设计(06-06)

- 基于Virtex 系列FPGA的可编程嵌入式信号处理背板的开发设计(06-06)

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)