基于DSP的FPGA配置方法研究与实现

时间:03-30

来源:互联网

点击:

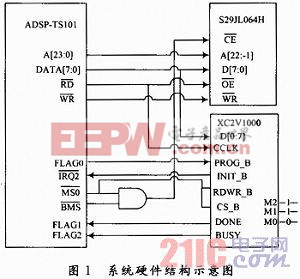

系统的硬件结构示意图如图1所示。由DSP的RD信号充当FPGA的配置时钟CCLK,FLAG0信号模拟FPGA的PROG_B信号,FLAG1和FLAG2分别作为FPGA的DONE信号和BUSY信号的输入。此系统在设计时,采用了DSP,FPGA,FLASH共用数据总线的方式,所以当DSP从FLASH芯片中读取FPGA的加载数据并出现在总线上的时候,可以直接被FPGA抓取来完成FPGA程序的正常加载。

2.2 工作时序

系统上电后,DSP启动DMA通道0,从FLASH地址0开始,把一个256 word的程序块传送到内部存储器地址0x00~0xFF。然后,DSP开始从0x00执行加载核,加载核将后续应用代码和数据加载至地址0xFF之后的内部存储器内。最后,加载核启动一个256 word的DMA,使其自身被工作程序代码覆盖。至此,DSP即从地址0x00开始执行工作程序。在工作程序中首先从FLASH存储器中读取FPGA的加载程序,并给出相应的加载时序,完成FPGA程序加载。具体的工作时序,如图2所示。

随着FPGA+DSP的系统结构在电子设计领域中应用的日益广泛化,在不增加其它额外器件的前提下,依靠DSP模拟FPGA加载时序,对FPGA使用了被动并行的配置方式。此方法在一定程度减少了设计冗余,实现了小型化和低成本。应用于电路系统中,工作稳定可靠,灵活高效。

- 基于ST7920的12864液晶的使用方法研究(02-19)

- 基于PGA的量程自动转换方法研究(01-09)

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- DSP中DMA操作的无阻塞请求实现(06-18)

- 二维DCT编码的DSP实现与优化(09-08)