PCI9052接口电路的功能及应用

对局部总线上的设备进行直接访问。PCI9052的配置寄存器将访问映射到局部地址空间。片内的读写FIFO存储器使PCI9052支持PCI总线与局部总线之间进行高性能的猝发传送。PCI总线主控访问局部总线示意图如图2所示。

图2 PCI主控直接访问局部示意图

3.6 PCI中断(INTA#)的产生

要产生PCI中断INTA#,首先将寄存器INTCSR[6](PCI中断使能位)设置为“1”,如果需要以软件方式产生中断,则只需将INTCSR[7](软件中断位)设置为“1”。如果系统设计方案中选用由局部总线上的设备产生中断信号INTi1和INTi2、再生成PCI中断INTA#的方式,只要将寄存器INTCSR的相关位按表1进行设置,复位后INTCSR的值全部为“0”。

表1 寄存器INTCSR相关的设置

4 应用实例

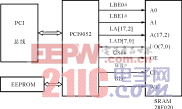

PCI9052是功能非常强大的PCI接口电路,用它设计PCI适配卡将使接口变得非常方便。图3是PCI主处理机读取SRAM的接口示意图,其主要功能是实现对RAM的单次或突发读、写操作。

4.1 电路连接

按照图3中的连接电路,对于SRAM主要有以下几个引脚:A(17,0)、I/O(7,0)、OE、CE、WE等。地址线A(17,2)与本地地址线LA[17,2]相连,根据PCI9052的LBE[0,3]#的定义,这里用8位数据总线将LBE0#与A0连接,LBE1#与A1连接,OE与PCI9052的CS0#相连。PCI9052为设计人员提供了4个片选信号CS(3:0)#,可以为4个设备提供片选信号,这样,可以避免设计人员在设计电路时设计片选解码电路,其地址和范围可由其对应的内部寄存内部本地寄存器配置。串行EEPROM用于存储配置寄存器内的配置信息,可以采用NM93C46或与之兼容的存储器。

4.2 寄存器设定

电路连接好后,要使电路能正常工作,必须对PCI9052内部寄存器进行配置。根据电路性能及特点,应将寄存器设定为非复用工作方式,采取存储器映射,8位数据总线。局部总线0的基地址寄存器值为240001H,其地址范围寄存器值为3FFF8H,其描述寄存器值为39H;片选0基址寄存器的初始值为4C0001;命令寄存器的初始值为02H;状态寄存器的初始值为800H,其他寄存器采用默认值。确定好各个寄存器的值后,应依据一定的次序将寄存器的初始值写入EEPROM。

4.3 驱动程序的开发

为了从PCI总线配置寄存器中获得主机动态分配的映射基址并对映射端口进行读写,必须编写驱动程序。编写Windows驱动程序时,可以使用DDK,但难度较大。为了简化驱动程序开发,可使用Jungo公司推出的WinDriver开发工具。WinDriver可自动生成VxD驱动程序及相应的高级函数。使用者不需具备Windows驱动程序开发知识,所生成的高级函数可直接在VC或CBuilder等高级编程语言中调用。

5 结论

实用证明,用专用PCI接口电路对设计PCI接口卡带来很大的方便。本文主要介绍PLX公司的PCI9052专用接口电路,设计者可根据需要选用其他接口电路,不需要ISA接口时,可选用PCI9050;需要DMA数据传送时,可选用PCI9054。专用接口电路是设计PCI适配卡的最佳方法,不但大大缩短了设计周期,而且有利于驱动程序的开发。

参考文献

[1]李贵山.戚德虎.PCI局部总线开发者指南[M].西安:西安电子科技大学出版社,1997.

[2]杨全胜.胡友彬.现代微机原理与接口技术[M].北京:电子工业出版社,2002.

[3]TomShanley,DonAnderson,刘晖译.PCI系统结构[M].北京:电子工业出版社,2000.

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- SHARC引领第四代通用DSP高端应用潮流(09-27)

- 在应用可编程测控网络设计(03-15)

- 基于dsPIC33F系列单片机的应用程序升级方法(04-03)

- 采用混合时钟模式提高Linux时钟精度的方法(05-10)

- MSP430低功耗原理及其在海温测量中的应用(06-06)