ARM/DSP多机I2C通信方案

引言

在很多嵌入式控制系统中,系统既要完成大量的信息采集和复杂的算法,又要实现精确的控制功能。采用运行有嵌入式Linux操作系统的ARM9微控制器完成信号采集及实现上层控制算法,并向DSP芯片发送上层算法得到控制参数,DSP芯片根据获得的参数和下层控制算法实现精确、可靠的闭环控制。

本文以Samsung公司的ARM9芯片S3C2440和TI公司的DSP芯片TMS320F28015为例,分析了I2C通信接口的原理及特点,提出了基于I2C总线的多机通信接口设计方法。测试结果验证了该系统的可行性及可靠性,对嵌入式系统设计具有一定的借鉴价值。

1 多机系统组成

该多机控制系统以ARM9微控制器s3c2440为核心,采用I2C总线挂载多个DSP芯片TMS320F28015作为协控制器,构成整个控制系统的核心。

1.1 S3C2440及TMS320F28015简介

Samsung公司的处理器S3C2440是内部集成了ARM公司ARM920T处理器内核的32位微控制器,资源丰富,带独立的16 KB的指令Cache和16 KB数据Cache,最高主频可达400 MHz.它拥有130个通用I/O、24个外部中断源以及丰富的外部接口能实现各种功能,包括支持多主功能的I2C总线接口、3路URAT、2路SPI、摄像头接口等。

TMS320F28015(以下简称F28015)是TI公司的32位处理器,它具有强大的控制和信号处理能力,能够实现复杂的控制算法。片上整合了Flash存储器、I2C总线模块、快速的A/D转换器、增强的CAN总线模块、事件管理器、正交编码电路接口及多通道缓冲串口等外设,此种整合能够方便地实现功能的扩展。同时,快速的中断响应使它能够保护关键的寄存器并快速(更小的中断延时)地响应外部异步事件。

1.2 I2C总线接口

I2C总线是一种用于IC器件之间连接的串行总线,采用SDA(数据线)和SCL(时钟线)两线连接每个带有I2C总线接口的器件或模块。串行的8位双向数据传输率在标准模式下可达100 kb/s,快速模式下可达400 kb/s.多个微控制器可以通过I2C总线接口非常方便地连接在一起构成系统,并根据地址识别每个器件。这种总线结构的连线和连接引脚少,器件间总线简单,结构紧凑。因此其构成系统的成本较低,并且在总线上增加器件不会影响系统的正常工作,所有的I2C总线器件共用一套总线,因此其系统修改和可扩展性好。

总线必须由主机(通常为微控制器)控制,主机产生串行时钟( SCL) 控制总线的数据传输,并产生起始和停止条件。SDA 线上的数据状态仅在SCL为低电平的期间才能改变,SCL为高电平的期间,SDA 状态的改变被用来表示起始和停止条件。I2C总线起始和停止时序如图1所示。

图1 I2C总线起始和停止时序

1.3 硬件电路

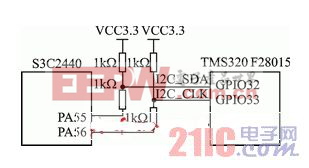

S3C2440和F28015自身均集成了I2C总线模块,支持多主设备I2C总线串行接口,可以方便地挂接到I2C总线上。因此,两者之间的I2C总线接口电路的设计变得十分简单,只要将两者的对应引脚I2C_CLK(对应I2C总线中的SCL线)和I2C_SDA(对应I2C总线中的DATA线)连接起来即可。S3C2440和TMS320F28015的硬件接口电路如图2所示。

图2 S3C2440和TMS320F28015的硬件接口

电路S3C2440的PA55和PA56引脚分别对应I2C_SDA和I2C_CLK,而F28015的GPIO32和GPIO33也可以分别复用为I2C_SDA和I2C_CLK.考虑到阻抗不匹配等因素会影响总线数据传输效果,因此在将两块芯片的I2C_DATA和I2C_CLK引脚直连时,在直连线路上各串联一个小电阻。

I2C_SDA和I2C_CLK是双向电路,必须都通过一个电流源或上拉电阻连接到正电源电压上。由于S3C2440和F28015的输出高电平均为3.3 V,所以在硬件设计时将I2C_SDA和I2C_CLK总线通过上拉电阻连接到了3.3 V的VCC电源上。

2 ARM和DSP通信软件设计

运行Linux操作系统的ARM微控制器作为主控制器,在数据管理及多任务调度等方面有显着优势,可以很好地组织外围器件采集的数据;主要实现对系统的整体控制,并通过总线设备驱动程序控制I2C总线模块,通过主机寻址实现向I2C总线上挂载的下层DSP的数据收发。为保证数据通信的实时性,F28015通过中断响应的方式实现数据接收和发送。

2.1 ARM9平台的嵌入式Linux的I2C总线驱动设计

2.1.1 I2C总线读写时序

ARM9微控制器作为主机向从机DSP写数据,首先向从机发送启动信号,然后发送7位从机地址和1位写标志位,再等待从机的应答信号。在收到应答信号后,主机发送数据给从机,再次等待应答信号。当主机收到应答信号之后再次发送数据。之后,主机等待从机的应答信号,如此直到数据发送完成,主机发送停止信号。I2C总线写数据帧格式如图3所示。

- SN2005学习系统 数字语音室解决方案(05-19)

- 以可编程DSP架构应对TD-SCDMA以及TD-LTE带来的设计挑战 (02-14)

- ARM-μCLinux嵌入式系统启动引导的实现(07-26)

- 多核处理器架构及调试方案(03-28)

- 基于DSP的电源解决方案(06-13)

- 间歇性Bug最佳解决方案(09-24)