基于I2C总线的CMOS图像传感器接口电路设计

中,它的低六位用来表示高24位的3个字节的属性,以便正确的传输,通过这种数据组合,便于I2C总线传输和识别。串-并转换和并-串转换本质上是两个移位寄存器,用来将接收到的串行数据转变成并行数据或并行数据转变成要发送的串行数据。

SDA产生接收器用宋生成主总线的控制命令如开始、结束和应答位等(和SCL配合工作),随后接收和读取数据。SCL产生器用来产生I2C总线的时钟信号和控制命令信号(和SDA配合工作)。控制状态机主要负责控制整个I2C总线的流程,其状态图如图4所示。主要包括以下八个状态:IDLE(等待读取或写入数据)、LOAD(加载需要传输的数据)、START(发送开始信号)、WRRD(I2C总线处于读取或写入数据状态)、DECIDE(判决当前状态是读取数据还是写入数据)、WR_ACK(写应答)、RD_ACK(读应答)、STOP(发送结束信号)。例如给CMOS图像传感器的一个寄存器写一个字节的数据,需要经历以下状态:IDLE→LOAD→START→WRRD→WR_ACK→WRRD→WR_ACK→WRRD→WR_ACK→STOP→IDLE;一个字节的写操作的ActiveHDL的仿真时序如图5所示。

3.3可编程降采样模块

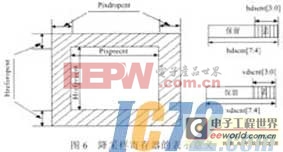

可编程降采样模块是通过MCU给内部的降采样寄存器写入需要的降采样参数来实现可编程的,接口内一共有6个降采样参数寄存器:总行数寄存器(hrefprecnt)、总列数寄存器(pixprecnt)、行丢寄存器(hrefdropcnt)、列丢寄存器(pixdropcnt)、行降采样寄存器(vdscnt)、列降采样寄存器(hdscnt),各个寄存器参数所表示的意义如图6所示。操作过程如下:先跳过列丢寄存器值和行丢寄存器值数目的列和行,接下来保留总列数寄存器值和总行数寄存器值数目的列和行,在这些保留的行和列当中用列降采样寄存器和行降采样寄存器的值进行降采样:行降采样寄存器和列降采样寄存器分为两部分:保留和丢弃,保留和丢弃的像素和行的数目均为偶数且为连续的像素,从而保证降采样后输出的像素满足RGRG…RG或GBGB…GB的Bayer格式。通过这样几个降采样寄存器可以很方便实现的各种分辨率的降采样,能够输出任意4的倍数的分辨率的图像,因而可以很方便的支持多种规格的LCD显示器。

4电路的FPGA验证

在经过上述顶层设计和各个子模块的设计后,用Verilog语言[5]来实现,并用ActiveHDL来进行RTL级仿真,并对电路进行了FPGA验证,使用的芯片是Xilinx公司的SPARTANIIXC2S200PQ208,系统时钟为54MHz,FPGA综合的结果显示需要FPGA芯片的11%的SLICEs,22%的IOBs和25%的GCLKIOBs。整个测试流程由MCU控制,在拍照模式下,CMOS图像传感器的数据流经CMOS接口采样存储在SDRAM中,再由EPP接口上传至PC上:在取景模式下,则有LCD显示器实时显示。该接口电路在各种工作模式下功能验证正确。

FPGA验证通过后,作为数码相机专用集成电路芯片的一部分采用上华0.6μm工艺库进行了ASIC的后端自动综合,包括用DesignCompiler(Synopsys公司)进行逻辑综合、PrimeTime(Synopsys公司)做版图前验证、SiliconEnsemble(Cadence公司)做自动布局布线、Virtuoso(Cadence公司)做DRC和LVS,最后得到的版图面积约为3.7mm×3.7mm,综合频率为25MHz,在5V供电下,功耗约为150mW。

5结论

CMOS图像传感器接口电路的设计模块可以分为寄存器文件、主12C总线接口和可编程降采样模块3部分,经过电路的顶层设计和各个子模块的功能设计,进行了Verilog语言代码实现,用ActiveHDL进行了RTL级仿真,并进行了FPGA验证,功能设汁正确,并打算作为数码相机专用集成电路芯片的一部分到工艺厂流片。

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- I2C总线及EEPROM的Linux驱动程序的设计(01-05)

- 基于C语言的I2C总线软件模块设计(01-09)

- 基于MSP430单片机的智能IC卡水表控制器(07-08)

- 实战经验吐血推荐:怎样在Linux环境下轻松实现基于I2C总线的EEPROM驱动程序(07-25)

- 基于FPGA的嵌入式图像采集系统设计(06-05)