针对Motorola微处理器的BDM调试系统的设计

目前应用Motorola微处理器开发嵌入式系统时基本上都是使用Motorola公司提供的开发系统或者CodeWarrior公司的开发系统等付费昂贵的调试工具。最近由于Flash技术的发展,特别是一些CPU(如CPU12/16/32/32+,PowerPC5xx/8xx,ColdFire等)可以用JTAG口在背景模式下调试,故仿真器已可以省去。而且随着BDM调试模式逐渐标准化,自制BDM调试工具变得越来越容易,特别是对于支持BDM调试模式的多种类型的CPU,自己设计的BDM调试系统只需少量的改动即可移植使用,而不必重复购买价格昂贵的调试开发系统,这样做可以节省大量的成本。

1 BDM调试模式介绍

Motorola微处理器的调试模块针对不同场合的应用分别提供了3种调试支持:实时跟踪、BDM调试和实时调试。实时跟踪是要求能够跟踪应用程序的动态执行路径,这是实时系统的基本要求;在BDM调试方式下,处理器被停机,大量的命令可以被发送到处理器中访问内存和寄存器,外部仿真系统使用一个三脚、串行的双工通道与处理器通信;实时调试则可以不需要CPU停止运行,调试中断允许实时系统执行一个惟一的服务例程,快速保存主要的寄存器和变量等上下文内容,并使系统立即返回到正常操作,外部的开发系统能访问被保存的数据是因为硬件支持处理器和BDM初始化命令的一致性操作。

其中BDM调试模式为设计人员提供了一种低层次的调试手段,让用户能够中断CPU的运行,单步调试程序,读取CPU的各个寄存器的内容,这些仅仅是通过向CPU发送几个简单的命令就可以实现,显然,这样使调试软件的设计很简单,通常自己就可以编写。硬件调试卡的设计也非常简单,关键是要满足好通信时序关系和电平转换要求。

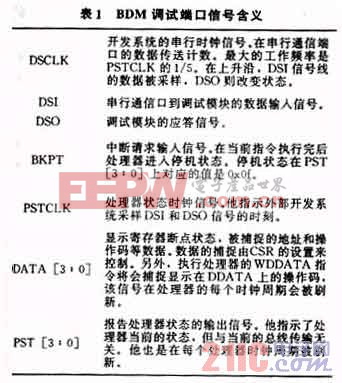

这几种调试方式都共用26脚的BDM调试引脚信号,这些信号的定义如表1所示,BDM调试主要使用了DSCLK,DSI,DSO三种信号。

|

2 BDM调试系统的运行条件及其系统组成

(1)系统运行的限制条件

尽管许多BDM命令可以与处理器并行操作,但是要想安全可靠地使用BDM操作,最好的方法就是让处理器停止运行。但是停机操作对于那些要求实时响应的应用程序的调试显然不理想。但是由于实时跟踪和实时调试模块与BDM调试模块引脚共用,所以升级和扩展BDM调试系统,可以很容易支持实时应用程序的调试。

(2)BDM调试系统组成

该系统主要由3个部分组成,如图1所示。

|

BDM调试卡作用是完成从并口到BDM调试端口(信号定义如表1所示)的操作时序的转换;BDM调试卡的驱动程序则是完成开发系统与待开发的嵌入式系统的通信过程处理,如合成一定格式的数据包、解释接收到的应答数据或者微处理器的状态数据等;BDM调试软件则是功能软件,完成读写指定位置的Flash或者SRAM数据、暂停、复位等功能。

值得注意的是,由于现在BDM调试模块的标准化,调试卡和驱动程序在不同型号的CPU上将具有通用性,只是BDM调试软件需要根据各种CPU对应的指令集来稍加修改即可复用。下面将以作者开发的一个针对Motorola公司的32位单片机MCF5272设计BDM调试系统的过程进行论述。

3 CodeFire系列处理器MCF5272的BDM调试系统的设计

3.1 BDM调试卡设计

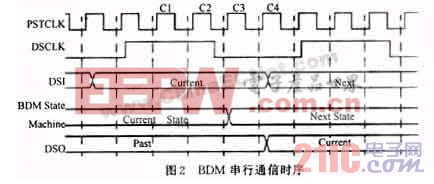

BDM接口的串行操作时序分析如图2所示。从图2中可以看出,在调试模块的串行状态机中所有的事件是基于处理器时钟(PSTCLK)的上升沿的。DSCLK的频率是PSTCLK的1/5,并且DSCLK的上升沿相对于PSTCLK的上升沿有一定的延时。这里的 DSCLK的作用类似于周期性的使能信号。每一次串行数据的传输可分为4个阶段:C1,C2,C3和C4。在DSCLK的高电平期间,数据从DSI输入,经过2个PSTCLK周期的同步(C1和C2)而被采样,然后在DSCLK的低电平期间PSTCLK的第1个上升沿处(C3)来临时BDM状态机改变状态,随后在第2个PSTCLK上升沿(C4),DSI准备传送新的数据,DSO上则输出原来数据输入相对应的应答数据。BDM状态机在DSI上数据采样检测到的时候改变状态,当所有的数据传输完毕,BDM状态机的状态也就不会有什么改变。

|

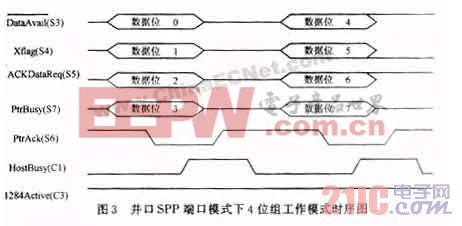

根据BDM端口的信号定义,不难看出这些信号都是单向的。其中要注意的是:PSTCLK是调试模块从处理器中获取的,而DSCLK则是外部的开发系统产生的。要实现从并口到BDM口的时序操作转换,最简单的方式是使并口工作在SPP端口模式下的4位组模式,在该模式下每次通过状态端口的4个状态位反向传送半个字节,两次传输完成向PC机传送一个字节数据[1]。他的操作时序如图3所示。

|

由于所有的信号都是单向的,时序和逻辑比较简单,因此,采用GAL器件实现并口操作时序与BDM操作时序的转换。GAL要实现的功能主要是数据的串并和并串转换。

GAL器件与并口接口的信号有:

输入信号:D0~D7,C1(主机忙状态线),DSCLK(提供串行通信时钟信号)。

输出信号:S3,S4,S5,S7(这4个信号做数据反向输出),S6(给PC机提供一个中断信号)。

他与BDM端口接口的信号有:

输入信号:PSTCLK,DSO。

输出信号:DSI。

故需配置12个输入端和6个输出端,故选用74GAL16V8的器件即可满足要求[2]。现在GAL器件要实现的即是将与并口接口的输入信号(D0~D7,C1,DSCLK)转换成与BDM接口的输出信号(DSI),同理,也要将与BDM端口接口的输入信号(PSTCLK,DSO)转换成与并口接口的输出信号(S3,S4,S5,S6,S7),实现了这2个转换,然后对GAL编程,设计PCB版图,可以很快做出BDM调试卡。

3.2 BDM驱动程序的设计

BDM调试卡已经实现了并口到BDM口的时序操作转换,按照一定的数据格式传送和接收数据则是BDM调试卡的驱动程序要完成的工作,驱动程序对数据的处理分为2层:底层完成基本的字节数据的收发(恢复和拆分);上层则完成数据包的收发。底层的数据收发原理在调试卡的设计过程中已经做了详细的介绍,以下主要介绍数据包的收发处理程序设计应注意的事项。

从BDM操作时序图中可以看出,串行通道数据传输速度从直流到PSTCLK频率的1/5频率之间,该通道使用双工模式,数据可在主控设备和从控设备之间同时发送和接收,每次传送的数据块由一个17 b的数据包组成,该数据包由一个状态/控制位和一个16 b数据字组成。数据格式如下所示:

系统 设计 调试 BDM Motorola 微处理器 针对 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)