单片机的扩展RAM读写时序实验

时间:05-02

来源:互联网

点击:

书上看到的毕竟是理论的东西,实际应用中总会碰上意外的或者说是不可预测的情况,与其在那瞎推理,还不如动手做点实际的工作。

特权同学用的是11.0592MHz的STC89C52做测试,C代码也很简单:

#include

#define uchar unsigned char

#define uint unsigned int

uchar xdata LD _at_ 0x7fff;

void delay(uint cnt)

{

uint i;

for(i=0;i

}

void main(void)

{

uchar i;

delay(1000);

while(1)

{

LD = 0x00;

LD = 0xf0;

LD = 0x73;

// i = LD;

delay(1000);

LD = 0xff;

delay(1000);

}

}

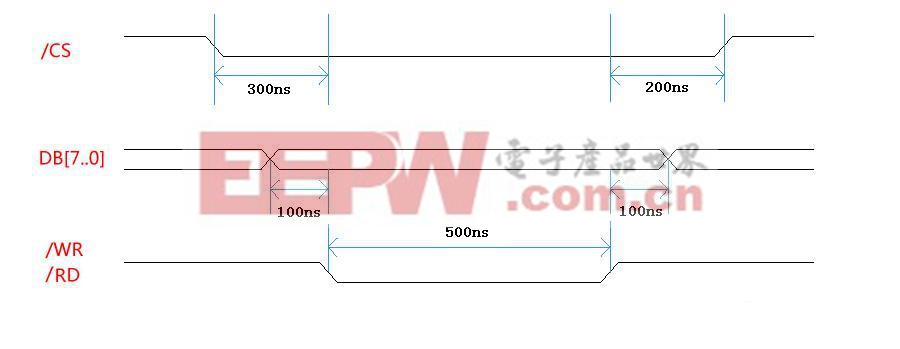

LD就是扩展的外部RAM变量,地址是0x7fff,也就是说P2的最高位就是CS信号。示波器测试了P0口任意一个数据的变化、CS的变化、WRRD信号的变化。大体整理了一下,波形基本如下:

另外,除了第一次LD读操作需要5个指令周期外(1.085us*5),以后每次LD读操作都只要3个指令周期(1.085*3)。这也是从汇编的代码里仿真后得出来的结论。而从上图也可以知道CS有效时间其实是一个指令周期(1.085us)。平均3个指令周期完成一次数据传输(所谓的RAM方式读写数据),这应该是单片机和外部通信的最快速度了。

- CPLD在DSP系统中的应用设计(04-11)

- 基于C语言的I2C总线软件模块设计(01-09)

- Verilog HDL基础之:时序逻辑电路(06-05)

- FPGA系统设计的仿真验证之: 功能仿真和时序仿真的区别和实现方法(06-05)

- 基于CPLD及钨铼热电偶温度传感器的爆炸场温度动态测试(06-05)

- SOC时序分析中的跳变点分析(06-05)