容错系统中的自校验技术及实现方法

摘要:阐述了自校验技术在容错系统中的作用,给出了自校验网络实现原理及实现方法,指出用VHDL语言结合FPGA/CPLD是实现大规模自校验网络的有效途径。

关键词:容错自校验完全自校验VHDLFPGA/CPLD

容错是容忍错误的简称,容错系统是指在发生硬件故障或存在软件错误的情况下,仍能继续正确完成指定任务的系统。设计与分析容错系统的各种技术称为容错技术。有关计算机容错技术的各种理论及研究已经发展成为计算机学科的一个重要分支,称为容错计算(Fault-tolerantComputing)。设计容错系统的指导思想是:系统发生故障时能自动检出并使系统自动恢复正常运行。

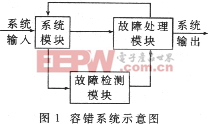

为保证系统具有高可靠、长寿命和响应迅速,必须采用容错技术。从功能上讲,一个容错系统可用图1所示框图来描述,系统模块可由若干个功能相同的子模块并联组成,故障检测模块对系统模块的功能进行检测,检测到故障后由故障处理模块对系统模块进行重新配置,使系统在部分模块失效的情况下,仍能输出正确结果。在这个系统中,故障检测模块和故障处理模块起着至关重要的作用,它们往往是系统的薄弱点。因此,容错系统要有高的可靠性必须保证故障检测和处理模块的可靠性,故障检测系统不仅要检测系统模块的故障,而且还要能够检测自身的故障,使故障处理模块得以正确处理所发生的故障。

自校验技术是用于故障快速检测的一种有效手段,特别是具有完全自校验性质的自校验装置,它不仅能及时检出系统模块的差错,还能检测出自身的差错。在容错系统设计中,将自校验网络置于系统中,可大大提高系统对差错的反应能力,使差错潜伏期缩短,有效地防止错误传播。

1自校验网络定义

一个容错系统,其所有可能的输出值组成的集合U(称输出空间)由S和U-S两部分组成。当系统中无故障时,系统输出S中的元素,一旦系统发生故障则输出U-S中的元素。

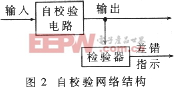

如果一个电路的正常输出集S是一个检错码集,则该电路称为自校验电路。在无故障发生的情况下,自校验电路输出码向量;当预定故障发生时,则输出非码向量。连接在自校验电路输出端的校验器监督电路的输出,当非码向量出现时,校验器给出差错指示。自校验电路与校验器一起构成了自校验网络,其结构如图2所示。

下面我们给出自校验网络的几个概念,设S(X)是输入向量空间,

是合法输入向量空间,

是非法输入向量空间,S(F)是输出向量空间,

是合法输出向量空间,

是非法输出向量空间,

是组合逻辑网络所考虑的单故障集,网络的所有输入取自其合法输入集。

定义1:组合逻辑网络对

是自测试的(简称ST),若:对任意故障

存在

,使网络输出

。

该定义是说对给定单故障集中的任何一个故障,总存在一个合法输入,它将导致组合逻辑网络产生非法输出,即用该输入可检测此故障。

定义2:组合逻辑网络对

是故障保险的(简称FSE),若:对任意故障

存在

使网络输出

,或者

,其中G(X)是网络的正确输出。

该定义是说在合法输入条件下,对给定单故障集中的任何一个故障,组合逻辑网络将给出一个合法输出或一个非法输出,但不会给出同该合法输入不相对应的另一个合法输出。

定义3:组合逻辑网络对

是完全自校验的,若它对

是自测试的和故障保险的。

对给定单故障集中的任何一个故障,完全自校验的组合逻辑网络在合法输入的情况下,或者产生一个合法输出,或者产生一个非法输出,且后者在故障存在期间是必然要出现的。这就使得网络在不产生不正确合法输出的同时,能并发检测

中的所有故障,这也正是在线测试对差错检测及时性的要求。

若采用检错编码技术实现自校验逻辑网络时,校验器的任务是用来检查功能模块输出码字的有效性,它能区分功能模块输出是否合法,这种特性被称为码分离特性,其定义如下。

定义4:一个逻辑网络具有码分离特性,若满足:

(1)任给

,有

(合法输入映射为合法输出)

(2)任给

,有

(非法输入映射为非法输出)

定义5:一个逻辑网络是完全自校验器,若它具有完全自校验及码分离特性。

设组合逻辑网络正确输入矢量为

,则矢量空间

称作错误输入空间,记作

;空间

被称作非法及错误输入空间,记作

。由正确输入空间

经电路G可在S(F)中产生一个子空间,这个子空间称为正确输出空间,记为

。同样,对于合法输入

,由组合逻辑网络可映射为合法输出空间

它也是输出矢量空间S(F)的子集。同样,空间

被称作错误输出空间,记作

;空间

被称为非法及错误输出空间,表示为

。上述输出之间有如下关系:

由上面集合之间的关系我们可以看出,对于无故障组合网络的正确输入,其输出应落入正确输出空间

中。通过对网络的输出可部分判定系

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- DSP中DMA操作的无阻塞请求实现(06-18)

- 二维DCT编码的DSP实现与优化(09-08)

- 基于DSP处理器上并行实现ATR算法(01-29)

- 基于DSP的H.324终端设计(05-27)