基于片内WISHBONE总线的高速缓存一致性实现

E空间发生的读写操作,过程如下所述:

读缺失:当一个内核的数据高速缓存发生读缺失,由本地主接口通过片内总线向远端数据高速缓存发出读请求,远端从接口通过片内总线应答请求。如果应答有该单元数据,就由远端数据高速缓存调来一个数据块(8个字);如果没有,本地主接口结束片内总线周期,转而访问外部总线,由主存调人数据。

写缺失:内核发生写缺失时,前半部分的操作与读缺失完全一致;只是如果缺失单元是从远端数据高速缓存调来的,由于采用基于写更新的Dragon协议,所以在完成片内总线块传输事务后还要产生一个单字写总线事务,更新远端数据高速缓存单元。

读命中:不会产生任何总线事务。

写命中:如果该单元的原来状态是SC或SM,基于写更新协议,由本地主接口通过片内总线向远端数据高速缓存发出写请求,远端从接口通过片内总线应答请求。如果应答有该单元数据,则通过一个单字写总线事务更新远端数据高速缓存单元;如果没有,结束片内总线周期。

替换:实现写回协议,只有被替换出的单元状态为SM或M状态,才通过外部总线更新主存,其他情况抛弃即可。

注意:完成上述操作后要根据DRAGON协议,更新本地和远端DCahe单元的相关状态。

3总线事务时序分析

由前部分的说明发现在内部总线上可以产生三种类型的总线事务:读缺失时,块传输总线事务;SM或SC状态写命中时,发生单宇写总线事务;写缺失时,先是一个块传输总线事务而后在本地写操作完成后,一个单字写总线事务更新远端的数据高速缓存单元。以下是块传输和单字写总线周期具体的时序分析,下文提到的具体信号其意义可以查阅参考文献[1]。

块传输时序:主接口通过声明CYC_O申请总线的使用权,同时也给出STB_O、CTI_0(010)、WE_O(低电平)和ADR_O;经过若干时钟周期等待后,如果远端从接口给出ACK_I信号,同时给出的SHARE_I信号为低电平(说明远端数据高速缓存没有所需要的数据块,.SHARE_I为自定义的信号),这时主接口忽略DAT-I信号,下一个时钟周期撤销CYC_O信号,结束片内总线周期;如果给出AClI信号的同时,SHARE_I信号为高电平(说明远端数据高速缓存有所需要的数据块),接收DAT-I上的数据;而后7个时钟周期内,每个时钟周期ADR_O数据加4,DAII上的数据根据地址相应地变化,在第7个数据传输的时钟周期CTI_O变为111,告诉远端从接口这是最后一个传输时钟周期,下一个时钟周期:降完成这个总线事务;最后一个时钟周期主接口撤销CYC_O信号,结束片内总线周期。

内块传输时序见图2。

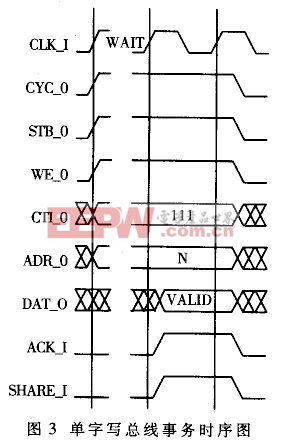

单字写总线周期:主接口通过声明CYC_O申请总线的使用权,同时也给出STB_O、CTI_O(111)、WE_O(高电子)、ADlO和DAT-0;经过若干时钟周期等待后,如果远端从接口给出ACK_I信号,同时给出的SHARE信号为低电子(说明远端数据高速缓存没有所需要的数_I据块),主接口下一个时钟周期撤销CYC_O信号,结束片内总线周期;如果给出ACK_I信号的同时,SHARK-I信号为高电子(说明远端数据高速缓存有所需要的数据块),说明从接口已经用DAT-O上的数据更新了相应的数据单元,下一个时钟周期撤销CYC_O信号,结束片内总线周期。

单字写时序见图3。

块传输总线事务时序图2,单字写总线事务时序图3中WAIT表示主接口等待总线仲裁和从接口的应答,需若干时钟周期,最快的情况下只要一个时钟周期。总线仲裁:如果两个数据高速缓存的主接口同时请求,由仲裁单元决定哪个主接口可以使用片内总线,仲裁的优先级算法是轮换法。数据高速缓存的主接口,在声明CYC_O申请总线后,如果AClI一直是低电平无效,但同时该数据高速缓存从接口的CYC_I信号有效,说明数据高速缓存主接口没有得到总线使用权,主接口撤销CYC_O信号,该数据高速缓存响应从接口的操作,操作完成后,主接口再次声明CYC_O信号请求总线;相反,如果数据高速缓存主接口的ACK_I信号高电平有效,说明得到了总线使用权,可以使用总线。

综上所述,片内总线采用WISHBONE总线地址增量的传输方式,与内核时钟同步,最快可以在9个时钟周期从另一个数据高速缓存调来一个块(8个宇)的内容,可在2个时钟周期更新远端数据高速缓存的一个相关单元;数据高速缓存实现写回、写更新机制,减少了向外部总线写操作的频度。该结构具有可扩展性,只要把片内WISHBONE·总线的地址线的位数扩展(用于选择多个从接口)就可以把多个内核集成在该芯片上,协议无需变化。该种体系结构运行两个耦合度很低的程序,性能最好。

该方案利用WISHBONE总线,基于监听总线的写更新一致性协议,把两个IP核集成在一块芯片上,实现了单芯片多处理器结构的

一致性 实现 高速 总线 WISHBONE 基于 相关文章:

- 基于C64x+ DSP高速缓存一致性分析与维护(03-01)

- 高速串行总线知多少…(12-13)

- 片上嵌入式多处理器的一致性机制设计(07-12)

- 分布式嵌入系统中的交互一致性(03-14)

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)