高速串行总线知多少…

时间:12-13

来源:互联网

点击:

纵观整个电子行业,制造商和其他公司推出的串行总线标准以满足市场和客户提出的多样化的需求。这些标准的关键性目标是在某一个体系框架内,由不同制造商生产的设备能够相互通用。每个标准是由一个管理机构、委员会和工作组,建立设计和测试要求。表1列出一些关键串行标准。

表1:重要的串行总线标准

表1:重要的串行总线标准

每个规范定义了产品必须符合标准的要求,包括电气、光学、机械、互连等等。管理机构发起标准化测试,来检验产品是否能通过标准要求。这些测试可能会详细到了指定具体的测试设备。标准不断发展,因此参数规格不断的修改。必须保持目前对产品的测试和规范的要求一致。

我参与许多标准组织并在不同的工作组中和其他公司一道,帮助管理机构制定有效的测试过程和符合性测试流程。

在这份文档中,我们会提到以下三个标准。泰克公司作为工作组的一员,参与到这些标准的制定中。

SATA

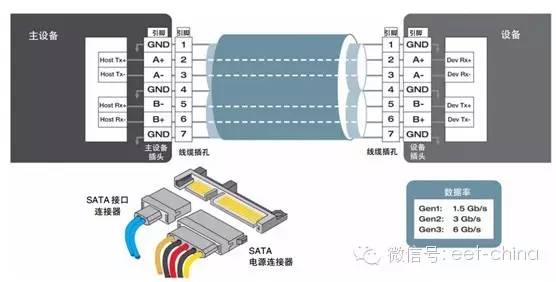

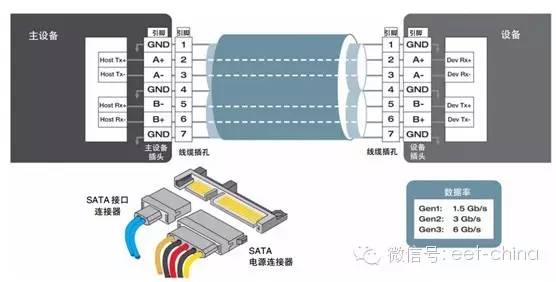

SATA接口是一个标准的串行存储接口,广泛应用于在今天的台式机和其他计算平台。最初的速率只用 1.

5Gbps,但最近更新到 3.0Gbps 的第二代规范,已经进入市场。下一代标准规定速率是 6Gbps,部分规范正在业内制定中。

图1.SATA总线的机械结构

图1.SATA总线的机械结构

像 许多串行标准,S A T A 接口采用低电压差分信号(LVDS)和8b/10b编码。数据在发射端和接收端之间采用全双工的数据通道,分别由一条发送通道(Tx)和一条接收通道 (Rx)组成。SATA 接口采用了扩频时钟(SSC)嵌入式时钟方法,不提供单独的参考时钟传送给接收端。

PCI Express

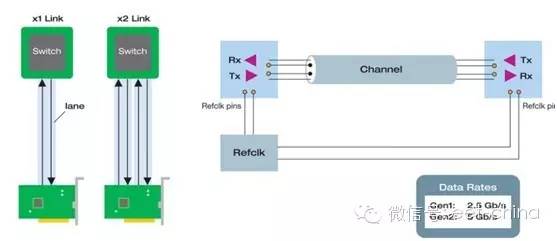

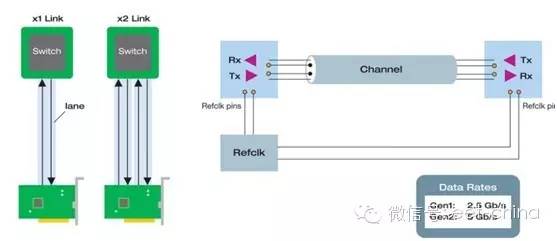

PCI Express已经取代PCI成为大多数芯片到芯片级的应用或电路板传输和电缆连接中系统中使用。PCIe 是一个高度可扩展的架构,提供从1到16条全双工的PCIe连接。在多通道应用,数据流根据现有可用通道的情况而拆分,同时在多个通道上传输。最快的 PCIe 应用通常是图像处理应用,通过 16条高速通道,在系统芯片组和图形处理器之间传输高分辨率的图形数据。图2描述了 PCI Express 架构。

图2.PCI Express架构

图2.PCI Express架构

第一代的每条通道传输速率是 2.5Gbps,第二代 PCIe2.0提供5Gbps的速率。很快第三代PCI Express提供8Gbps 的传输速率。PCIe 不仅采用嵌入的时钟,还将参考时钟传输到接收端作为 PLL 参考时钟。

HDMI

高清多媒体接口(HDMI)是第一个专为满足消费娱乐系统市场而推出的串行总线标准。HDMI接口建立在非常成功的数字视频接口(DVI)之上,并延伸了更多功能,集成了更多的娱乐设备,如大屏幕、高清电视和家庭影院系统。图 3 描述了 HDMI 接口架构。

图3.HDMI架构

图3.HDMI架构

HDMI 是一个单向传输的架构,从源端向接收端传送高分辨率视频和多声道音频。该规范定义了三个高速串行数据通道,根据显示分辨率,传输速率从250 Mbps到3.4 Gbps 不等。为了追求更高的数据速率和更高的分辨率,在机械部分规格定义了 Type B 型连接器,将两个 HDMI 接口并联,产生了最大吞吐量为 6.8Gbps 的数据流。

虽然大多数高速串行标准依靠 LVDS 信号格式和 8b/10b编码,但HDMI接口使用的是过渡时间最小化差分信号(TMDS),以减少链接上信号的跳变,从而减少电磁干扰(EMI) 。

HDM 接口采用了参考时钟的设计,时钟频率为数据率的十分之一。低速串行总线 (I2C总线),称为DDC的总线,在源端和接收端进行配置和识别时进行双向信号传输。

串行总线结构的基本要素

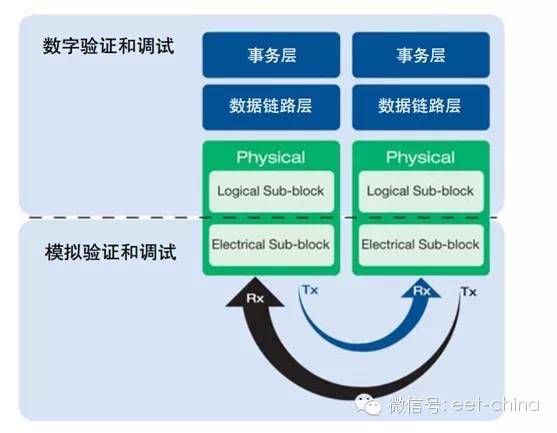

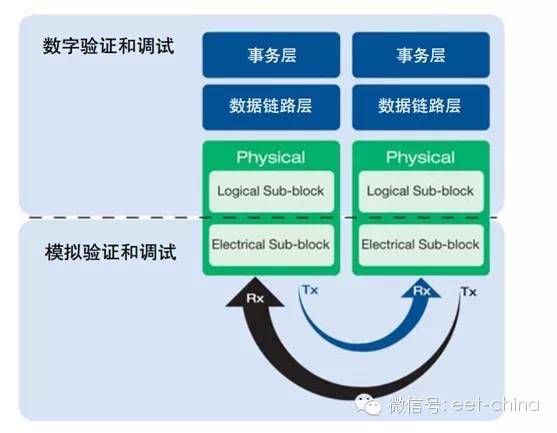

所有的串行总线结构遵循一个多层模型,正如图 4 所示。物理层有电气子层和逻辑子层构成。本文主要讨论的是电气子层上所进行的一致性测试。

图4.速串行总线分层模型

图4.速串行总线分层模型

很多高速串行标准的电气子层有如下要点:

◆差分信号传输,提供良好抗干扰能力

◆8b/10b 编码减小 EMI,改善信号完整性

◆嵌入式时钟和参考时钟一起使用

◆通过扩频时钟进一步减小时钟的 EMI 问题

◆典型的测量包含抖动、幅度、差分对间延时、上升 /下降时间和共模电压

◆规范和测试需求随着标准不断发展而演进

表 2:串行总线构架要素总结

表 2:串行总线构架要素总结

表1:重要的串行总线标准

表1:重要的串行总线标准每个规范定义了产品必须符合标准的要求,包括电气、光学、机械、互连等等。管理机构发起标准化测试,来检验产品是否能通过标准要求。这些测试可能会详细到了指定具体的测试设备。标准不断发展,因此参数规格不断的修改。必须保持目前对产品的测试和规范的要求一致。

我参与许多标准组织并在不同的工作组中和其他公司一道,帮助管理机构制定有效的测试过程和符合性测试流程。

在这份文档中,我们会提到以下三个标准。泰克公司作为工作组的一员,参与到这些标准的制定中。

SATA

SATA接口是一个标准的串行存储接口,广泛应用于在今天的台式机和其他计算平台。最初的速率只用 1.

5Gbps,但最近更新到 3.0Gbps 的第二代规范,已经进入市场。下一代标准规定速率是 6Gbps,部分规范正在业内制定中。

图1.SATA总线的机械结构

图1.SATA总线的机械结构像 许多串行标准,S A T A 接口采用低电压差分信号(LVDS)和8b/10b编码。数据在发射端和接收端之间采用全双工的数据通道,分别由一条发送通道(Tx)和一条接收通道 (Rx)组成。SATA 接口采用了扩频时钟(SSC)嵌入式时钟方法,不提供单独的参考时钟传送给接收端。

PCI Express

PCI Express已经取代PCI成为大多数芯片到芯片级的应用或电路板传输和电缆连接中系统中使用。PCIe 是一个高度可扩展的架构,提供从1到16条全双工的PCIe连接。在多通道应用,数据流根据现有可用通道的情况而拆分,同时在多个通道上传输。最快的 PCIe 应用通常是图像处理应用,通过 16条高速通道,在系统芯片组和图形处理器之间传输高分辨率的图形数据。图2描述了 PCI Express 架构。

图2.PCI Express架构

图2.PCI Express架构第一代的每条通道传输速率是 2.5Gbps,第二代 PCIe2.0提供5Gbps的速率。很快第三代PCI Express提供8Gbps 的传输速率。PCIe 不仅采用嵌入的时钟,还将参考时钟传输到接收端作为 PLL 参考时钟。

HDMI

高清多媒体接口(HDMI)是第一个专为满足消费娱乐系统市场而推出的串行总线标准。HDMI接口建立在非常成功的数字视频接口(DVI)之上,并延伸了更多功能,集成了更多的娱乐设备,如大屏幕、高清电视和家庭影院系统。图 3 描述了 HDMI 接口架构。

图3.HDMI架构

图3.HDMI架构HDMI 是一个单向传输的架构,从源端向接收端传送高分辨率视频和多声道音频。该规范定义了三个高速串行数据通道,根据显示分辨率,传输速率从250 Mbps到3.4 Gbps 不等。为了追求更高的数据速率和更高的分辨率,在机械部分规格定义了 Type B 型连接器,将两个 HDMI 接口并联,产生了最大吞吐量为 6.8Gbps 的数据流。

虽然大多数高速串行标准依靠 LVDS 信号格式和 8b/10b编码,但HDMI接口使用的是过渡时间最小化差分信号(TMDS),以减少链接上信号的跳变,从而减少电磁干扰(EMI) 。

HDM 接口采用了参考时钟的设计,时钟频率为数据率的十分之一。低速串行总线 (I2C总线),称为DDC的总线,在源端和接收端进行配置和识别时进行双向信号传输。

串行总线结构的基本要素

所有的串行总线结构遵循一个多层模型,正如图 4 所示。物理层有电气子层和逻辑子层构成。本文主要讨论的是电气子层上所进行的一致性测试。

图4.速串行总线分层模型

图4.速串行总线分层模型很多高速串行标准的电气子层有如下要点:

◆差分信号传输,提供良好抗干扰能力

◆8b/10b 编码减小 EMI,改善信号完整性

◆嵌入式时钟和参考时钟一起使用

◆通过扩频时钟进一步减小时钟的 EMI 问题

◆典型的测量包含抖动、幅度、差分对间延时、上升 /下降时间和共模电压

◆规范和测试需求随着标准不断发展而演进

表 2:串行总线构架要素总结

表 2:串行总线构架要素总结 高速串行总线一致性测 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)