基于RTAI的嵌入式Linux硬实时性能的研究与实现

操作系统 | 方波最小周期 | 任务的最小周期约 |

uClinux | 40.002 ms | 20 ms |

RTAI/uClinux双内核 | 110.19 us | 55 us |

表1 时间分辨率实验结果分析表

Table1 Analysis of the time resolution experiment

例如,在RTAI-uClinux系统中在不同的定时周期下的实验波形图如图3图4所示。当定时周期较大时系统稳定运行,而过小的定时周期(50us)会使系统运行变得不稳定。

图3 定时周期大于100微妙时的试验波形图

Fig3 Oscillogram of the system output when cycle > 100us

图4 定时周期小于50微妙时的试验波形图

Fig4 Oscillogram of the system output when cycle 50us

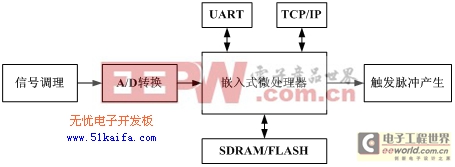

从实验结果可以看出,uClinux操作系统难以完成周期小于20ms以下的周期性任务,因此对于周期性的A/D采样以及高实时控制很难实现,经过改造后的RTAI/uClinux双内核结构时间分辨率低于100us,完全可以满足电能质量控制器在A/D采样等方面的实时性周期任务。

3.3 中断响应速度测试

中断的响应速度是实时控制系统的重要指标,例如在A/D采样和计算完成后,系统需要控制进程尽快地被调度执行,以执行正确的控制策略。对于一个支持硬实时任务的系统来说,除了测试系统的平均响应速度外,还需要测试系统在最差情况下的响应速度以及处理器的负荷状况对系统响应速度的影响。

设计实验如下:利用一个外部的DSP帮助测量系统的中断响应速度。DSP2407在启动内部定时器后,将MCF5249 的一个I/O引脚状态改变,MCF5249内部的高优先级进程在引脚状态改变并且被重新调度后,立即将DSP2407的指定I/O引脚置高,DSP2407在其指定的I/O引脚被置高后停止定时器。利用DSP2407的定时器可以精确的计算出从MCF5249引脚状态改变至MCF5249 内部进程响应之间的时间间隔,从而确定MCF5249内部进程的响应速度。改变MCF5249处理器的负荷,重复实验,在每种情况下重复实验过程1000 次,找出不同情况下系统响应的平均速度以及最慢响应速度。

操作系统 | 处理器负荷轻 | 处理器负荷较重 | ||

平均响应时间 | 最慢响应时间 | 平均响应时间 | 最慢响应时间 | |

uClinux | 120us | 12ms | 221ms | 795ms |

RTAI/uClinux | 25us | 27us | 27us | 30us |

表2 响应速度实验结果分析表

Table2 Analysis of response speed experiment

从实验结果可以看出,在处理

- 嵌入式Linux技术在工业控制网络中的应用(10-30)

- 基于嵌入式Linux的组态软件实时数据库的设计(02-01)

- 基于ARM+DSP的嵌入式Linux数控系统设计(11-18)

- 基于嵌入式Linux的细胞特征提取算法设计(11-19)

- 基于S3C2410的嵌入式Linux系统构建(03-02)

- 嵌入式Linux网络编程之:网络基础编程(08-13)