基于16位单片机的家电信息监测系统方案设计的

从目前的情况看,大部分接入方式仍以PC作为网关来连接,然而这种情况一般用于大型工业集散控制系统,如果用于一般的信息家电接入而额外增加一台,必然会给产品带来高昂的成本,从产品的经济实用方面来看并不切实可行。用嵌入式设备将信息家电接入的方式则很好地解决了这一问题。 随着网络时代的到来,internet已成为重要的基础信息设施,这方面的技术进步对于社会的各个方面产生了积极影响,很多领域都在不断探索开发和利用网络资源。所谓嵌入式设备一般是由嵌入式微处理器、外围设备、特定的网络协议以及应用程序等各部分组成,用于实现对信息家电的远程控制、监视和管理功能,它代替了传统的PC机或网关设备,在数据量不大的情况下能够符合要求,具有可靠灵活、成本低等优点。

方案的提出

从信息家电远程在线访问的角度考虑,对信息家电监测和控制时存在两种情况:

(1)远程访问时,信息家电的通信数据量不大,56Kbps的通信速率即可满足要求;

(2)信息家电对实时性的要求不高,其时延可以在1秒以上。基于以上两个条件在选择嵌入式设备时,选择了单片机SPCE061A作为信息家电接入internet的微处理器,同时采用RTL8019AS作为以太帧的驱动芯片,负责以太帧的接收和发送。最后,通过RJ45接口发送状态信息到internet和接收来自internet的控制数据.此外,要实现信息家电接入internet还需要深入了解TCP/IP协议和网卡驱动程序。

RTL8019AS以太网控制器简介

由台湾Realtek公司生产的RTL8019AS以太网控制器,由于其优良的性能、低廉的价格,使其在市场上10Mbps网卡中占有相当的比例。

2.1主要性能

(1)符合EthernetII与IEEE802.3(10Base5、10Base2、10BaseT)标准;

(2)全双工,收发可同时达到10Mbps的速率;

(3)内置16KB的SRAM,用于收发缓冲,降低对主处理器的速度要求;

(4)支持8/16位数据总线,8个中断申请线以及16个I/0基地址选择;

(5)支持UTP、AUI、BNC自动检测,还支持对10BaseT拓扑结构的自动极性修正;

(6)允许4个诊断LED引脚可编程输出;

(7)100脚的TQFP封装,缩小了PCB尺寸。

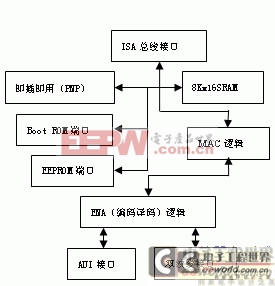

RTL8019AS内部可分为远程DMA接口、本地DMA接口、MAC(介质访问控制)逻辑、数据编码解码逻辑和其他端口。其内部结构如图1所示。

图1RTL8019AS内部结构

ISA总线接口即远程DMA接口,是指主机对RTL8019AS进行控制和操作的总线,本地DMA接口是指RTL8019AS与网线的连接通道,作用是完成控制器和网络线的数据交换。PNP(即插即用)逻辑部分主要是用来解决和PC机的连接问题,BootROM端口作用是解决远程启动问题;EEPROM端口是用来操作RTL8019AS和EEPROM芯片24C64的接口,SRAM用来存放接收和要发送的数据;MAC逻辑完成数据的发送和接收过程中的一些控制;当主机要发送数据时,将一帧数据经过远程DMA信道送到以太网络控制器中的发送缓存内存中,然后发出传送命令,以太网络控制器在送出前一帧的数据后继而完成此帧的发送;接收数据时,串行数据组成字节送到FIFO和CRC,发送逻辑将FIFO送来的字节在发送时脉的控制下逐步按位移出并送到CRC,CRC逻辑在接收时对输入的数据进行CRC校验,将结果与帧尾的CRC比较,如不同该帧数据将被拒收,如相同则送到接收缓冲区中。等到接收缓冲区收满一帧后以中断或缓存器标志的方式通知主处理器把数据读走。

2.2RTL8019AS的I/O地址分配

以太网络控制器内建的16KB的SRAM,可划分为接收缓冲区和发送缓冲区两个部分,缓冲区以帧为单位,每页256个字节,16KB的SRAM的页范围规定在0x40—0x80,由PSTART和PSTOP寄存器来设定接收缓冲页的范围,CURR指向接收到的帧的起始页,BNRY指向还未读取的帧之起始页亦即下一帧的页地址,当CURR到达了接收缓冲页的底部即与PSTOP相等时CURR又会自动指到PSTART处,因此这16KB的SRAM是设计成环状缓冲区的,以达到可再使用的目的。

硬件描述

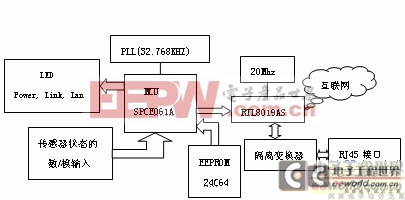

整个系统的设计核心是台湾凌阳科技股份有限公司推出的具有总线结构的16位高性能CMOS微处理器,可以进行高速运算、灵活的I/O口控制和高效的数据操作。SPCE061A具有2K字的SRAM和32K字的闪存ROM.与现有的8位微处理器相比,其提供了速度较高的16位x16位乘法运算指令Mul和内积运算指令Muls,加上优化的指令集,SPCE061A的吞吐量大为提高,这使得精简的指令集能够在其中可靠运行。系统硬件电路组成框图如图2所示。

图2系统硬件电路框图

该硬件结构主要包括两部分:1.反映信息家电工作状态的信息采集2.数据经过TCP/IP协议压缩后,通过以太网控制芯片输出到internet,或接收来自internet的控制数据并进行解包。该系统基于IEEE1451.2和T

- Freescale 16位单片机的地址映射(11-28)

- Freescale 16位单片机命名参考规则(11-23)

- 凌阳16位单片机之用时基中断定时(11-20)

- 凌阳16位单片机之IRQ4中断(11-20)

- 凌阳16位单片机之定时器中断(11-20)

- 凌阳16位单片机之IRQ6中断(11-20)