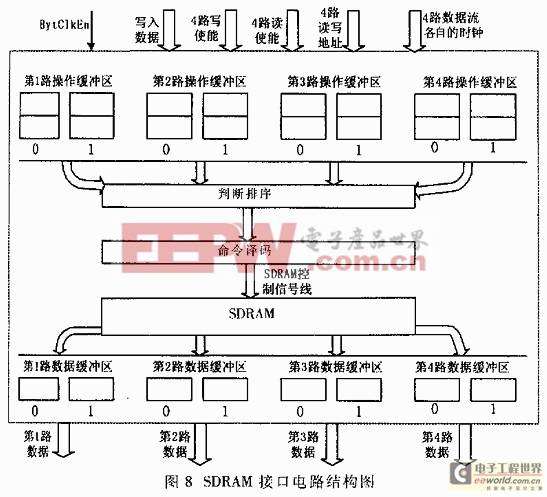

多路读写的SDRAM接口设计

时间:06-06

来源:互联网

点击:

- μClinux下SDRAM数据交换区的生成和使用(06-04)

- 基于DSP的数码望远相机的研究与设计(03-28)

- DSP片外高速海量SDRAM存储系统设计(01-18)

- 基于DSP片外高速海置SDRAM存储系统设计(03-12)

- DSP片外高速海置SDRAM存储系统设计方案(06-13)

- FPGA最小系统之:最小系统的概念(06-05)