采用NioslI的SOPC系统的LCD显示驱动IP核方案设计

器、8位列地址寄存器,以及32位数据寄存器等。

3.3 Ayalon总线接口

显示驱动的Avalon总线接口需要一个简单的Slave端口。该端口使用较少的Avalon信号来处理简单的寄存器读/写传输。该模块是与Avalon总线接口的一个顶层模块,主要功能是对任务逻辑模块和寄存器模块进行例化和封装,使其信号类型符合Avalon总线信号规范和外接模块的信号规范。顶层接口定义如下:

3.4 显示驱动封装及软件设计

直接在SOPC Builder中添加设计好的显示驱动IP Core和Verilog HDL语言描述的文件,并根据Avalon总线传输规范设置好相关的信号线及传输参数。由于是在NiosII IDE环境下直接编写用户程序,可以不用编写驱动程序。完成后,将显示驱动IP Core添加至SOPC工程,并编译、下载到FPGA器件中。

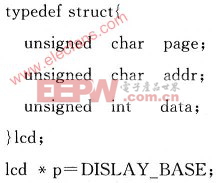

在NiosII IDE环境下,使用自己添加的模块编写程序,可直接调用甬数IOWR(BASE,OFFSET,DATA)和IORD(BASE,OFFSET)对内部寄存器进行读写。本文使用结构体定义了一个指向模块的结构体指针,对寄存器进行读写操作。

CBGl28064本身不带字库,可以通过2种方式添加字库:一种是把所需字库做到硬件ROM中,增加了硬件资源成本,且缺乏灵活性;另一种是在软件中定义字库,通过写数据寄存器进行显示。本设计采用第2种方式,在软件中定义字库,并编写了简单的显示测试程序,在液晶屏上显示“ZHONG GUO”字样。测试结果表明,该设计是正确可行的。此外,利用字模软件生成的图形数据,也可进行图形显示。

结语

本文采用有限状态机设计了CBGl28064液晶模块驱动硬件逻辑,并将显示驱动IP核进行封装构成了一个模块化的独立元件,使其能够在其他的工程中复用;在此基础上,基于NiosII嵌入式处理器构建了一个用户定制的片上系统。经过在Cyclone系列FPGA上测试,该驱动能够在C-BGl28064液晶模块上显示字符、图形。整个系统体现了SOPC嵌入式系统的灵活性和扩展性。

驱动 IP 方案设计 显示 LCD NioslI SOPC 系统 采用 相关文章:

- 声卡安装向导中文版(11-12)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- Linux内核解读入门(11-09)

- Linux操作系统网络驱动程序编写(04-11)

- Linux系统下USB摄像头驱动程序开发(04-25)

- Linux系统中如何正确安装摄像头驱动(04-25)