采用VHDL和发接复用器的SDH系统设计及FPGA仿真

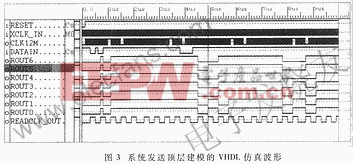

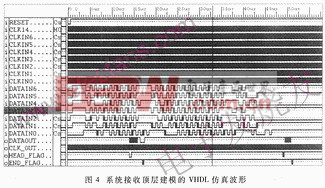

nto 0)-2.048 MHz 7 route -output data; ); end TRAN_TOP; (2)系统发送顶层建模的VHDL仿真波形 ROUT0:0,0111111110(插入的SYNC)1011111,0(每7bit固定插入‘0’)10,111…(空闲码) ROUT1:0,0111111110(插入的SYNC)1011111,0(每7bit固定插入‘0’)10,111…(空闲码) ROUT2:0,0111111110(插入的SYNC)0111111,0(每7bit固定插入‘0’)10,111…(空闲码) ROUT3:0,0111111110(插入的SYNC)0111111,0(每7bit固定插入‘0’)10,111…(空闲码) ROUT4:0,0111111110(插入的SYNC)0111111,0(每7bit固定插入‘0’)00,111…(空闲码) ROUT5:0,0111111110(插入的SYNC)1111111,0(每7bit固定插入‘0’)01,111…(空闲码) ROUT6:0,0111111110(插入的SYNC)0111111,0(每7bit固定插入‘0’)0,1111…(空闲码) 这样,从仿真波形可知电路完成了每帧二进制10M数据分接为7路2M数据时在每路2M数据中插入SYNC(0111111110)、每7bit固定插入‘0’以及在10M数据每帧分接完后插入全1空闲码的操作。 (3)系统接收顶层建模的VHDL端口描述 Library IEEE; Use IEEE.std_logic_1164.all; --引用库说明; Entity RCV_TOP is Port (RESET:IN STD_LOGIC; --system reset signal; XCLK : IN STD_LOGIC: --14.336MHz input high clock; CLKIN: IN STD_LOGIC_VECTOR(6 DOWNTO 0); --2.048MHz 7 rout input clock; DATAIN:IN STD_LOGIC_VECTOR(6 DOWNTO 0); --2.048MHz 7 rout input data; CLK_OUT:OUT STD-LOGIC; --12.544MHz output clock; DATAOUT:OUT STD_LOGIC; --12.544MHz output data; ); end RCV_TOP; (4)系统接收顶层建模的VHDL仿真波形 如图4所示。7路包含有SYNC(0111111110)及每7bit插入‘0’的两帧2M数据通过接收系统被正确地复接为10M数据。HEAD_FLAG和END_FLAG分别为复接帧数据的帧头帧尾指示信号。 这时的7路仿真数据相互之间的延迟不同,其中第DATAIN0延迟最大(8bit),通过系统仿真可以证明7路2M数据间的延迟差最大可到125bit,远远起过技术要求的1~6bit。这样,从系统上确保了设计的可行性。 3.2 状态转移图设计方法 为去除毛刺,本设计中的计数器全部采用格雷码计数器。因为格雷码计数器从前一个状态到后一个状态的变化同时只有一位矢量发生状态反转(如:对于一个 8位计数器它的计数状态变化是:000→001→011→010→110→111→101→100),故对它译码时可以防止竞争冒险现象,从而消除了电路在译码时可能产生的刺。对于有大量状态转移的电路,采用状态转换图输入法方便、直观;在FOUNDATION工具中,状态图输入又可以转化为VHDL语言,这又大大提高了电路设计的灵活性。 4 功能仿真、后仿真和FPGA实现 本设计采用自顶向下(top-down)的设计方法。但为确保设计的可行性,对于每一个子模块都进行了功能仿真和后仿真。用foundation工具做功能仿真时,电路中没有器件延时和线延迟,只能从电路的功能上验证设计的正确性;而后仿零点能模拟实际电路中的器件延时和线延时,从而能进一步验证设计在实际工作中的正确性。最后本设计在FPGA(Xilinx Spartan XCS30TQ144)实现,其工作频率可达到20MHz,并在SDH系统的光纤环网上通过了测试。 5 FPGA验证及问题讨论 (1)FPGA验证时的7路2M数据间的延迟差 为了验证7路数据在传输中有不同延时,分接复用器依然能正常工作,就需要模拟出7路不同的延时来。有三种不同的实现方法来完成:·这7路不同的延时可以在FPGA内中用不同的非门串起来实现; ·可以采用74系列器件在FPGA外部完成不同延时的模拟; ·在FPGA内部用不同级数的D触发器来模拟7路不同的延时。 在本设计中采用的是第三种。该方法的好处是易于控制不同路的延时,只要改变不同路中D触发器的级数就可以改变7路不同的延时。 (2)为提高分接复用器的传输效率,可采用不固定插“0”法,例如HDLC中的插“0”法 (3)可以通过在综合时进一步加约束来提高分接复用器的工作频率。 本文中的分接复用器为系统通信提供了灵活的速率选择。可根据不同需要,以2Mbps为基数来配置各种数据速率。本设计中采用VHDL输入法及状态图输入法,大大缩短了设计周期,提高了设

如图3所示,送来的10M二进制的一帧数据(DATAIN)为“1100010001(帧头)1111111111,1111111111,1111111111,11111111,1000000001 (帧尾)”。把分接为7路2M的数据如下:

设计 FPGA 仿真 系统 SDH VHDL 复用器 采用 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)