DSP与AD转换器的接口电路设计

摘要:在以DSP为核心的数字信号处理系统中,模数转换是系统重要的组成部分。作者以德州仪器公司的TMS320C6203B与ADS5422为例,详细说明了DSP与AD转换器的接口电路设计方法。最后还介绍了DSP控制数据采集的软件流程。

关键词:DSP;AD转换器;接几电路

0 引言

在以DSP为核心的数字信号处理系统中,AD转换是系统重要的组成部分。因为往往需要进行信号分析、处理的对象是模拟量,例如语音信号、各种传感器输出的模拟信号。这些信号经过放大、滤波及A/D转换后,从模拟信号转换为数字信号,再由DSP芯片对这些数字信号按照某种算法进行处理。

德州仪器公司(TI)的TMS320C6000系列DSP是目前广泛使用的数字信号处理芯片,相应地,TI公司提供了一系列与其DSP相配套的A/D、D/A转换器。本文以TI公司的TMS320C6203B型DSP与高速ADC—ADS5422为例,详细说明了DSP与AD转换器的接口电路设计方法以及DSP控制数据采集的软件程序流程。

1 TMS320C6203B型DSP简介

TMS320C6203B片内有8个并行的处理单元,分别为相同的两组。DSP的体系结构采用甚长指令字(VLIW)结构,单指令字长为32bit,8个指令组成一个指令包,总字长为256bit。芯片内部设置了专门的指令分配模块,可以将每个256bit的指令包同时分配到8个处理单元,并由8个单元同时运行。

该型DSP的最高时钟频率为300MHz,考虑到本系统高频电路的实际情况,设置时钟频率为250MHz,由于TMS320C6203B内部采用8条指令并行处理技术,这样使得DSP内部指令周期达到2GHz,可以满足ADS5422的采样速度要求。此外,DSP内部具有4Mbit的数据空间和3Mbit的程序空间,也满足数据采集系统数据存储的需要。

2 ADS5422型模数转换器简介

ADS5422的内部结构如图1所示,ADS5422的时钟信号由CLK从外部引入,由于ADS5422的内置时钟电路,使得ADS5422对各种时钟都兼容,包括正弦波或者方波、TTL电平或者CMOS电平、单端时钟信号或者差分时钟信号。外部模拟信号从IN和IN(-)引脚输入,首先经过一个高带宽的线性跟随器(T/H)单元,确保AD具有很高的无寄生动态响应,经过跟随器后的信号到达14位的直通型AD,将模拟信号转换为数字信号,同时ADS5422内部的梯度选择单元以及模式选择单元控制信号转变的方式,数字信号经过逻辑校验单元,到达三态数据输出寄存器输出。

ADS5422的最高采样频率为62Msample/s,具有14位并行接口,最高信噪比为72dB。可以采用差分或者单端模拟信号输入方式,输入电压峰峰值从2V到4V可选。该芯片采用单5V电源供电,数字量输出可以直接和5V或者3.3V的CMOS芯片连接,并且有单独的满量程标志引脚和有效信号输出引脚。

3 模拟信号输入电路

ADS5422的最高采样频率达到62MHz,模拟信号输入可以采取单端输入方式或者差分输入方式两种。本系统采取差分输入方式,可以尽量减少信号噪声以及电磁的干扰,尤其是采用差分输入方式可以将所有的偶次谐波通过正反两个输入信号基本上互相抵消。

ADS5422的模拟信号差分输入方式需要同时使用IN和 引脚,其硬件连接如图2所示。首先使用放大器OPA687以及RF变压器将单端信号转换成差分信号,然后输入ADS5422,其中ADS5422的公共端CM和RF变压器的公共端连接。为了增强信号的稳定性,在ADS5422的每个信号的输入前加上RC元件组成的低通滤波电路,图2中Rt为50 Ω,Rin为22 Ω,Cin为10pF。

引脚,其硬件连接如图2所示。首先使用放大器OPA687以及RF变压器将单端信号转换成差分信号,然后输入ADS5422,其中ADS5422的公共端CM和RF变压器的公共端连接。为了增强信号的稳定性,在ADS5422的每个信号的输入前加上RC元件组成的低通滤波电路,图2中Rt为50 Ω,Rin为22 Ω,Cin为10pF。

4 时钟输入电路

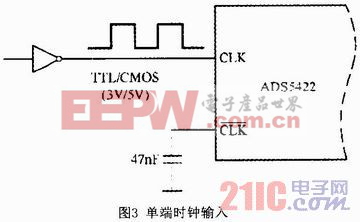

ADS5422的时钟输入也有单端和差分两种输入方式,对于单端输入方式,只需要将时钟信号连接到ADS5422的CLK引脚,CLK引脚通过电容接地就可以了。差分输入方式与模拟信号的差分输入方式基本上相同,同时还需要为一些必要的RC电路以及RF变压器去除噪声干扰。本系统采用单端输入方式,由DSP的定时器输出功能为ADS5422提供稳定的时钟信号,从而避免差分时钟输入所需要的一些外围电路。图3为单端时钟输入的连接图。

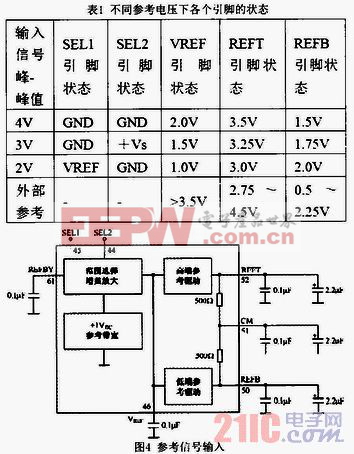

ADS5422有3种可选择的内部参考电压信号,分别为1V、1.5V和2V,对应模拟输入信号的峰-峰值为2V、3V和4V。内部参考电压的选择由SEL1和SEL2引脚确定,SEL1和SEL2引脚的状态决定参考电压引脚REFT、REFB以及VREF引脚的电压。表1为不同参考电压下各个引脚的状态。

6 模数转换器的采样和数据输出

6.1 采样

只需要提供给ADS5422时钟信号,ADS5422就会根据这个时钟信号开始采样。但由于ADS5422是高速AD,一般其输出的数据信号和模拟信号有10个时钟周期的延迟。还有一个需要注意的地方,就是该芯片启动的时间相当长,这也是高速AD转换器的普遍缺点。如果将一个60MHz的时钟输出到ADS5422,ADS5422就会马上开始采样,但此时的采样频率低于60MHz,然后缓慢地上升到60MHz,直至稳定。这是ADS5422的时钟建立时间,一般需要5ms。如果时钟为60MHz,则前500个采样数据的采样频率为未知,不能使用。ADS5422的采样时序如图5所示。图中所示各个时间如表2所示。

- 单片机做红外遥控解码器(06-20)

- 基于Multisim10的智能秒表设计(10-29)

- 特种单片开关电源模块的电路设计(10-15)

- 基于DSP的电子负载技术文献汇总(09-12)

- 基于PSD系列芯片的单片机电路设计(11-15)

- 基于单片机的电子琴的电路设计(10-14)