Redboot修改实例

在通常情况下,嵌入式开发中都需要对bootload部分的代码进行修改,以适应实际的需求。本文以redboot为例,说明了如何修改redboot源码以使其具备

1. 启动时提供LOGO图片显示

2. 为实现量产,在命令行下提供自动配置网络的命令autocONfig

3. 为实现量产,在命令行下提供自动更新文件的命令update

4. 为实现量产,在命令行下提供自动配置脚本的命令autoexec

Redboot适用的运行环境为基于ARM架构的硬件环境,包括

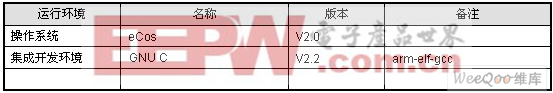

运行环境如下表所示。

Redboot是Red Hat公司开发的一个独立运行在嵌入式系统上的BootLoad程序,是目前比较流行的一个功能强大、可移植性好的BootLoad。

Redboot是一个采用eCos开发环境开发的应用程序,并采用了eCos的硬件抽象层作为基础,但它完全可以脱离eCos环境运行,并用来引导人和其他的嵌入式操作系统,如Linux、WinCE等。

eCos实现系统可配置机制的核心就在于它是由许多个组件构成,包括调度内核组件、硬件抽象层、文件系统组件、网络协议栈等,用户可以根据不同的需求选择组件,并对一些特定的配置选项进行设置,就可以构造出满足特定应用需求的系统。

所有的组件都在组件库中,组件库其实是一个包含了eCos所有系统组件的文件夹,其路径对应于“/eCos-2.0/packages”,该目录的内容如下所示

☆ compat

包含支持与POSIX和uITRON3.0标准兼容的组件文件包

☆ cygmon

生成Cygmon调试监视器的配置文件包

☆ devs

eCos支持的所有外部设备驱动,如串口、以太网等

☆ error

包含各种常见的错误和状态描述代码,便于系统调试时报告错误和状态

☆ fs

包含ROM和RAM文件系统包

☆ hal

包含所有硬件抽象层的目标硬件配置文件包

☆ infra

包含系统定义的基本结构,如数据类型、宏定义、系统启动方式选择

☆ io

I/O子系统文件包,建立在外部设备驱动上层从而与特定硬件无关

☆ isoinfra

包含的文件包提供支持ISO标准C库和兼容POSIX标准的接口

☆ kernel

提供eCos内核功能的配置文件包

☆ language

包含ISO的C库和math库

☆ net

提供TCP/IP协议栈支持的文件包

☆ redboot

包含生成Redboot调试监视器的配置文件包

☆ services

包含提供动态内存分配和文件压缩与解压功能的库文件

与硬件相关的文件按照如上所述,分别对应以下的子目录:

“/eCos-2.0/packages/hal/arm”:Architectur HAL

“/eCos-2.0/packages/hal/arm/arm9”:Variant HAL

“/eCos-2.0/packages/hal/arm/arm9/ep93xx”:Platform. HAL

为了实现本文开头的四项特殊功能,需要修改eCos中的部分代码。修改的文件为:

“/eCos-2.0/packages/hal/arm/arm9/ep93xx/v2_0/src/ep93xx_misc.c”

“/eCos-2.0/packages/redboot/v2_0/src/Flash.c”

“/eCos-2.0/packages/redboot/v2_0/src/io.c”

“/eCos-2.0/packages/redboot/v2_0/src/main.c”

ep93xx_misc的修改

在本例中,开发平台上添加了一块FPGA芯片,通过该FPGA实现了对LCD的控制,因此对于raSTer的初始化过程有所不同。

该部分的修改,主要目的是提供“启动时提供logo图片显示”的功能。

增加__FPGA_LCD__宏定义

增加_RASTER_宏定义

_RASTER_ 完成Raster设置并且显示开机界面。

_ FPGA_LCD _ 完成FPGA设置并且显示开机界面。

Raster:

initRaster用来初始化LCD controller

LCD 界面定制在Nor Flash AddrESS 0x60DC0000

Copy Kernel 到指定Address, Copy zImage 到0x800000(SDRAM Address)

FPGA:

1. check chip 分区是否存在

2. 如果存在则Copy logo and chip 到指定地址。

3. 初始化FGPA。

4. 显示开机界面。

5. Copy Kernel 到指定地址。

初始化FPGA流程:

1. Config相关GPIO

a) GPIO 0-7===D0~D7为输出

b) GPIO 9,11,12===PROG_B,CSI_B,CCLK为输出 8,10===DONE,INIT_B为输入

2. Clear相关SDRAM

a) set prog_b low to clear the config data

b) start the config process

c) ready to read the init_b status

3. 写Chip.bin

4. 显示logo

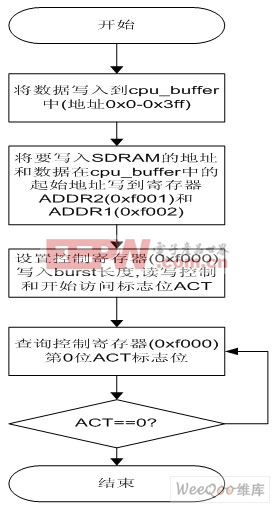

SDRAM write流程如下图所示:

1. 根据CPU_buffer的使用情况,将准备写入SDRAM的数据,先存入CPU_buffer中。

2. 然后需要依次配置ADDR1、ADDR0、CONTROL_REG。

3. cpu_sdram_cmdgen会根据以上寄存器的设置,将cpu_buffer中的数据发送至arbiter,后存入SDRAM.

4. 数据请求完成后,cpu_sdram_cmdgen会将CONTROL_REG.ACT自动清除。

5. CPU可以通过查询CONTROL_REG.ACT位,得知当前写入SDRAM数据的操作是否完成。

6. 写SDRAM步骤实例如下

a) write (16'h00F0, 16'haaaa);

b) write (16'h00F1, 16'hbbbb);

c)

- 国外现场总线应用实例两则(12-21)

- 三菱PLC编程技巧及实例图解(12-19)

- 单片机的七个创意设计实例(从易到难),附电路图、源代码、演示视频(06-11)

- PCI驱动程序开发实例(02-21)

- 51单片机做信号发生器实例编程(01-16)

- 简单的单片机I/O口扩展实例(05-18)