基于电子记帐控税终端机设计的片上系统SOC芯片研究

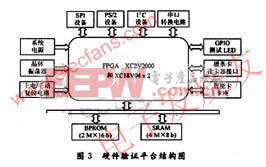

3.1 验证平台的设计 FPGA芯片;配置PROM;程序BPROM;SRAM;串口转换芯片;I2C总线设备;SPI总线设备;磁卡读卡器接口;智能卡及卡座;GPIO测试点;PS/2设备;系统时钟发生设备;上电复位电路;电源。

本SOC芯片内部采用AMBA总线,内嵌32 b整数处理单元,优化的32/64 b浮点数处理单元,并且内嵌了大量的外设,主要包括:80位GPIO口、4路UART控制器、5个24 b定时器、看门狗、.PS/2控制器、I2C总线控制器、SPI总线控制器、1个三磁道磁卡控制器,3个智能卡控制器等。为了完整地测试本SoC的所有功能,硬件测试平台如图3所示,包含下列基本组成部分:

3.2 FPGA平台验证结果

将由SoC的RTL模型产生的FPGA下载文件(*.bit文件)下载到FPGA中,在Unix环境下,用SPARC-GCC编译器编译测试程序(标准C程序),然后观察程序运行结果,就可以验证整个SoC系统或某一模块功能的正 确性。

下面以获取智能卡复位应答(Answer To Reset,ATR)字节为例,阐述此过程。

事先知道待测智能卡的ATR字节为:3b,7a,18,0,0,21,8,11,12,13,14,15,16,17,18。

测试结果为:

Smartcard controller testing…

ATR over,and ATR characters:

3b,7a,18,0,0,21,8,11,12,13,14,15,16,17,18

以上结果说明,智能卡控制器可以接收到卡的复位应答字节,SoC的此功能正确。采用同样的方法及过程可以验证其他功能的正确性。

4结 语

该SoC芯片如今已经成功应用到了多种电子记帐终端设备中,为国内外的电子记帐终端设备制造商们提供了一种高性价比的选择,为中国芯家族又增添了一位新成员。所以,可以认为该SoC芯片的设计还是非常成功的。

设计中存在的主要问题就是内置的RAM空间还不够大,对于高端的电子记帐终端设备,必须外扩一定容量的RAM存储器,希望在下一款同类芯片设计中加以改进。

SOC 芯片 研究 系统 设计 电子 记帐 终端机 基于 相关文章:

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)