ADSP-BF531在嵌入式语音识别系统中的应用

摘要:设计了一个嵌入式语音识别系统,该系统硬件平台以ADSP-BF531为核心,采用离散隐马尔可夫模型(DHMM)检测和识别算法完成了对非特定人的孤立词语音识别。试验结果表明,该系统对非特定人短词汇的综合识别率在90%以上。该系统具有小型、高速、可靠以及扩展性好等特点;可应用于许多特定场合,有很好的市场前景。文中讲述了该系统CODEC、片外RAM、ROM以及CPLD等与DSP的接口设计,语音识别运用的矢量量化、Mel倒谱参数、Viterbi等有关算法及其实际应用效果。

关键词:ADSP-BF531;语音识别;离散隐马尔可夫模型;非特定人;孤立词

自上世纪70年代以来,国内外的专家们在语音识别研究领域内取得了重大突破,先后出现了动态时间规整技术(DTW)、隐马尔可夫模型(HMM)和人工神经网络(ANN)等3种主要方法。DTW虽然在孤立词语音识别中取得了不错的性能,但其要求的存储量和计算量太大;ANN虽然前景看好但其目前尚未有突破性进展,目前它们都难以在工程中得到广泛的应用。HMM算法使语音识别的计算量得到大大减少,而且正确率较高,从而在语音识别中得到广泛引用。

笔者在以ADSP-BF531为核心构建的嵌入式系统上实现了对非特定人、孤立词的语音识别,该系统采用了端点检测、矢量量化(VQ)和离散隐马尔可夫模型(DHMM)等算法。

1 ADSP-BF531介绍

ADSP-BF531是ADI公司Blackfin系列的高性能DSP,其最高主频为400MHz,内有2个16位MAC,2个40位ALU,4个8位视频ALU,以及1个40位移位器,RISC式寄存器和指令模型,编程简单,编译环境友好。

BF531包含丰富的外设,通用外设如UART、带有PWM(脉冲宽度调制)和脉冲测量能力的定时器、通用的I/O标志引脚、以及一个实时时钟和一个“看门狗”定时器。它还有多个独立的DMA控制器,能够以最小的处理器内核开销完成自动的数据传输。DMA传输可以发生在ADSP-BF531处理器的内部存储器和任何有DMA能力的外设之间。此外,DMA传输也可以在任何有DMA能力的外设和已连接到外部存储器接口的外部设备之间完成(包括SDRAM控制器、异步存储器控制器)。具有DMA传输能力的外设包括SPORTS、SPI端口、UART和PPI端口。每个独立的有DMA能力的外设至少有一个专用DMA通道。

2 硬件电路设计

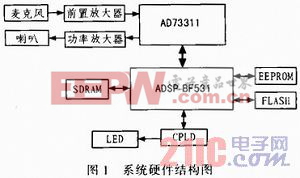

该系统电路主要由DSP、音频编码器、CPLD、片外SDRAM、FLASH和EEPROM存储器以及电源、时钟等组成。硬件接口如图1所示。

各器件的主要功能如下:

1)AD73311将经前置放大后的麦克风音频信号经A/D转换后通过串行端口输入BF531,同时完成对BF531输出的数字音频信号的D/A转换,而后输出到功放和喇叭;

2)BF531作为该系统的核心,对信号进行特征提取和DHMM识别,同时对其外围的器件进行控制管理;

3)CPLD完成对DSP的外围的器件时序和数据流程控制,以及对LCD显示屏初始化检测设置;

4)由于DSP片内的RAM有限,配置了一块SDRAM用于扩展系统的内存,以满足程序运行时数据和指令存储的要求;

5)EEPROM用于存放DSP程序代码和系统初始化所需的数据;

6)FLASH用于存放训练样本库。

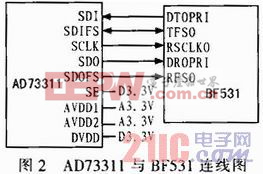

2.1 AD73311与BF531接口设计

本系统中设计AD73311的采样率为16 kHz,其与BF531的串口0(SPORT0)连接,通过DMA方式在单时钟周期内完成操作。BF531支持32 bit的串口数据传输,由于AD73311为16 bit的音频器件,而且16 bit已可满足系统精度要求,因此本系统只使用了BF531的主传输数据通道,即:DTOPRI和DROPRI,而将第二传输数据通道DTOSEC和DROSEC进行了屏蔽。AD73311与BF531的连接方式如图2所示。

2.2 SDRAM接口设计

SDRAM主要用于扩展系统内存,为保证程序运行的裕量及后续升级的需要,这里选用了三星电子的一款容量为32 MB的移动式SDRAM,其型号为K4M56163PG。SDRAM与DSP的I/O总线连接,如图3所示。

2.3 EEPROM接口设计

EEPROM主要用于存放程序代码,选用ATMEL公司的AT45DB161D-TU型的EEPROM,该型存储器采用SPI接口,容量为2 MB,可以满足程序存储的要求,其与DSP的SPI端口连接。

通过设置EEPROM存储器的SPI主模式启动(即设置BMODE=11),现实配置BF531为连接一个SPI存储器的主设备和存储器的加载。为了正常工作,该加载模式需要在MISO加上拉电阻。否则,BF531将从MISO引脚读取到0xFF(即SPI存储器没有写任何数据到MISO引脚)。不仅MISO线上的上拉电阻是必要的,额外的上、下拉电阻还有如下2个用途:

1)上拉PF2信号,确保SPI存储器存DSP复位状态下未激活;

2)在SPICLK上用下拉电阻,使显示画图更加清晰。

2.4 FLASH接口设计

片外FLASH主要用于存训练样本库,本系统采用的NANDFLASH为三星电子的K9F8G08U0M-PIB0,该FLASH为工业级SLC架构(Single Laver Cell,单层单元)芯片,具有速度快、可靠性高等特点,而且容量为1 GB,可以满足存储大量样本数据的要求。其采用EBIU(External Bus Interface Unit,外部数据总线)和单个GPIO(General Purpose Input Output,通用输入/输出引脚实现与DSP数据通讯。

3 软件设计

3.1 语音识别(孤立词)的原理

本系统采用的孤立词语音识别的原理框图如图4所示。

系统 应用 识别 语音 嵌入式 ADSP-BF531 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)