一种应用于OFDM系统中的符号精确定时算法的FPGA实现

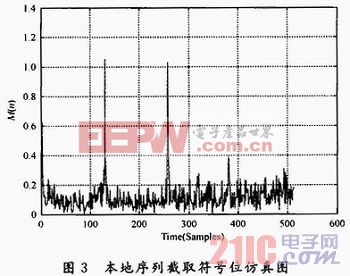

图3是采用本地序列截取2 b的判决函数M(n)的Matlah仿真图;图4是采用本地序列截取4 b的Matlab仿真图。检测峰值时,第一个峰值是由于循环前缀存在的影响,峰值检测时检测第二个峰值。

从图3,图4中可以看出,截位虽然会损耗算法的性能,但是判决函数存在明显峰值,选择适当的阈值时,仍然可以精确定时同步,可见减少本地序列的精度对性能并未造成很大的影响。

图5是采用判决函数取近似值的Matlab仿真图,图6是判决函数取确定值的Matlab仿真图。检测峰值时,第一个峰值是由于循环前缀存在的影响,峰值检测时检测第二个峰值。从图5,图6中可以看出,在判决函数近似处理虽然会损耗算法的性能,但是判决函数仍然存在明显峰值,选择适当的阈值时,仍然可以精确定时同步,可见减少对判决函数的近似对性能并未造成很大的影响。

表1是在AWGN环境下精同步位置的仿真结果,每个信噪比下经过5 000帧的仿真。符号同步偏差表示每个信噪比下的精同步平均错误长度,可见在系统的性能并未明显降低。

3.2 精同步模块实际实现

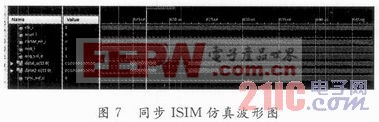

硬件设计是基于XLINX公司的SPRTAN6系列中的XC6SLX150-2FGG484芯片,采用Verilog HDL语言,仿真软件是ISE自带的ISIM,开发环境是ISE。

整个OFDM系统同步的ISIM仿真波形如图7所示。其中:clk_i表示时钟信号;reset_i表示同步复位信号;clk5M_en_i表示5 MHz时钟使能信号;nrst_j表示异步复位信号;acq_val_o表示粗捕获指示信号;dataI_o,dataQ_o表示经过粗捕获和粗频偏估计的输出信号;

sync_val_o表示精同步指示信号。

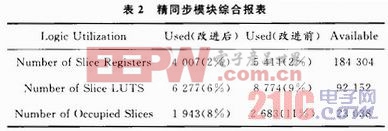

经过ISE综合后,改进前和改进后精同步占用资源分布如表2所示。

由表2可见本文对系统资源优化的效果十分明显。

4 结语

本文分析了一种OFDM系统精同步算法的原理,给出了FPGA硬件实现方案和结果分析,该方案在采用经典算法的同时,对算法进行了改进,在不降低精同步性能的前提下大大降低了计算复杂度,并且设计结构简单,易于实现,具有较好的工程实用价值。

- 水声OFDM系统中卷积码译码设计及其DSP实现(04-11)

- 一种基于Turbo 码的MIMO-OFDM检测系统的设计(05-15)

- 基于OFDM调制技术的配电自动化通信系统研究(11-30)

- PF-503数字移动微波在马拉松直播中的应用(10-12)

- OFDM系统的频域同步估计技术介绍(05-02)

- 一种基于DSP+FPGA的软件无线电平台的设计及应用(07-05)