抗SEU存储器的FPGA设计实现

时间:09-16

来源:互联网

点击:

法来进行电路的有效性验证,所以,在电路设计中,可将模式配置寄存器的其余14位用于注入外部干扰数据,并将其连接到ctrl_err与add_err信号,以用来进行软件故障的注入,模拟SEU对电路的影响。

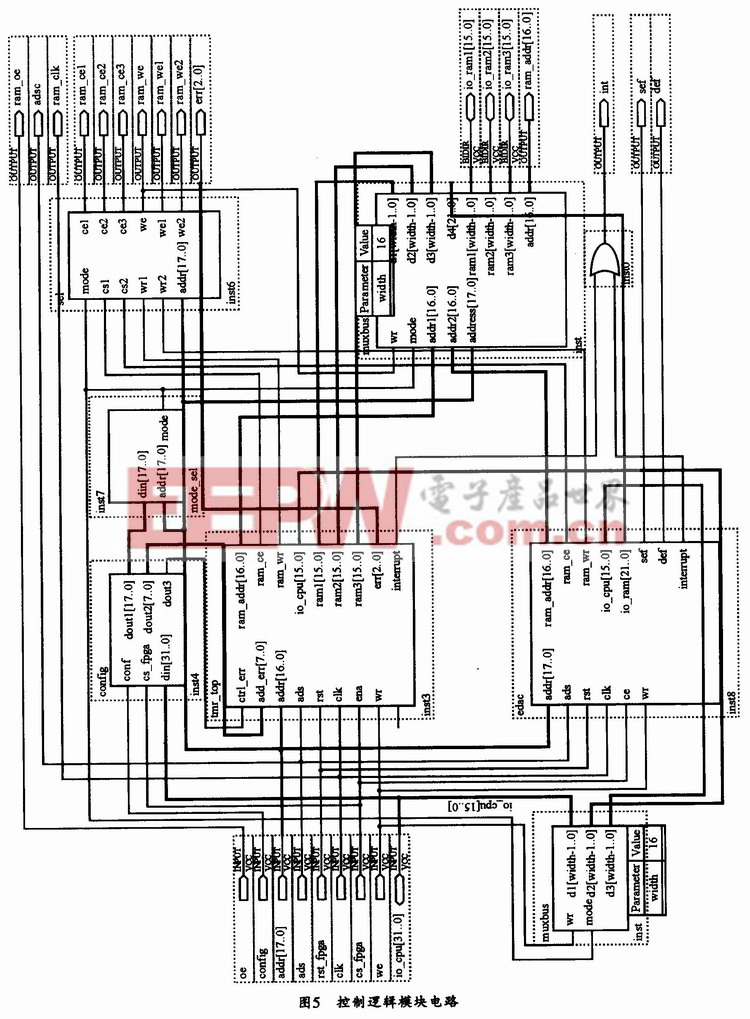

4.4 控制逻辑模块

该模块可接收模式选择模块的模式信号mode,以对TMR模块和扩展汉明码模块输出的读写信号和片选信号进行选择,然后输出到RAM芯片的引脚上去,从而实现CPU对RAM的正确访问。尤其是当电路工作于扩展汉明码模式时,还需根据地址信号判断当前对哪个124 Kx (16+8)bit的存储空间片选有效。其具体电路如图5所示。

5 结束语

本设计中的抗SEU存储器的设计可通过ACTEL的ProAsic系列A3P400 FPGA实现,并可使用与其配套的Liber08.5 EDA工具进行代码的编辑和原理图的绘制,并进行功能仿真与电路的综合。通过仿真可以看到,本设计可以达到预期的目的,它既可实现存储器的抗SEU设计,又可以满足对存储器使用灵活性的要求,而且具有功能完善、适应性强、电路简单等特点,非常适用于星载RAM的抗辐射电路设计。

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- DSP中DMA操作的无阻塞请求实现(06-18)

- 二维DCT编码的DSP实现与优化(09-08)

- 基于DSP处理器上并行实现ATR算法(01-29)

- 基于DSP的H.324终端设计(05-27)