基于FPGA的高速卷积硬件设计及实现

动增益(AGC)的作用,为了在连续输出模块中产生统一的比例,必须用最终的指数对FFT函数输出进行比例换算。

4 实际工程中的卷积的实现

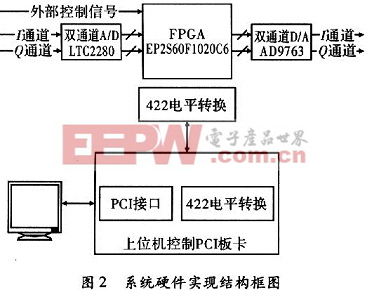

如图2所示,给出了一个实际应用的例子。为了保证I,Q两路的相位同一性,使用双通道A/D,选择Linear公司的LTC2280,LTC2280支持10 bit,105 Ms/s的最大采样率,并拥有61.6 dB的信噪比(SNR),85 dB的无杂散动态范围(SFDR),满足系统需要。双通道D/A使用Analog公司的AD9763,AD9763支持10 bit、125 Ms/s的最大采样率。

首先,需要在PC机上准备好h(n)对应的DFT变换结果H(k),H(k)的处理实际上有两种方法,一个是将h(n)下载到下位机中,使用下位机硬件实现H(k),还有就是将H(k)在上位机就计算好,直接将计算结果下到下位机中。由于h(n)在系统工作中是不变的,在PC机端事先计算好H(k)更合适,不仅可以减少FPGA的资源占用,而且也方便数据的处理。基于以上的考虑,本系统将在PC机端求出的H(k)通过422接口下载到下位机的RAM中,方便使用。

下位机系统工作之前,上位机需要通过PCI控制板卡将计算好的数据下载到下位机的RAM中,方便工作过程中的数据使用。在收到外部控制信号后,下位机开始启动,LTC2280开始采集I、Q通道数据并送入到FPGA中。

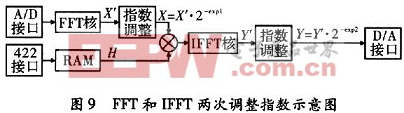

AD输出的I,Q数据直接作为一个复数的实部和虚部进入FFT核进行FFT变换。为了加速处理速度,使用基-4四引擎输出结构。FFT核输出的结果X(k)过指数调整以后直接进入到一个硬件复数乘法器,与存储于RAM中计算好的H(k)对应相乘,同时乘法器输出可以直接输入到IFFT模块进行逆FFT运算,IFFT计算结果再经过指数调整以后即可以直接通过D/A输出。

5 性能分析与改进

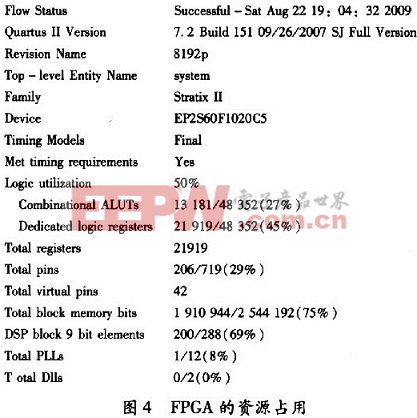

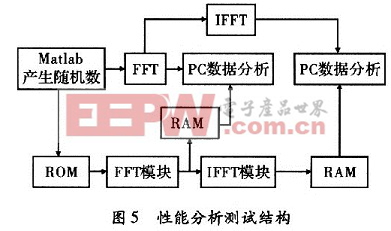

FPGA的流水线结构决定了速度的瓶颈取决于整个流程中处理速度最慢的部分。在FFT核速度可以保证的前提下(EP2S60的理论速度可以达到293.06 MHz),而处理过程中全部使用FPGA内部RAM来存储中间数据,所以在本系统中,FPGA内部的理论处理速度达到200 MHz以上。本系统的处理速度主要局限于A/D和D/A的数据转换率,根据实际测试,在100 MHz系统时钟下,数据吞吐率可达100 Ms/s,满足了设计技术指标。图4给出了FPGA的资源占用。为了较好地检测整个使用FFT_IFFT实现卷积的系统性能,设计了一个初略性能分析测试结构,如图5所示。

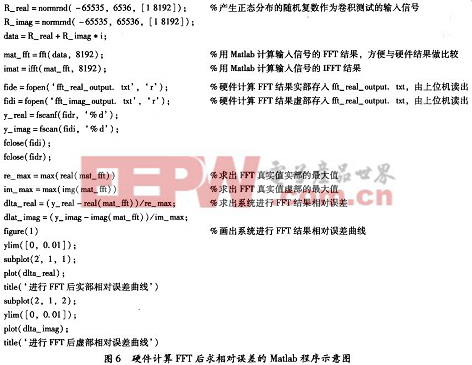

在图5中,由上位机产生的一组8 192点随机复数a(t)写入ROM中,作为FFT模块的信号输入,经过FFT后将结果B(ω)存入RAM中,以方便上位机读取并与a(t)使用Matlab计算出来的FFT结果A(ω)进行比较;接着将该FFT结果B(ω)再进行IFFT计算,由数字信号处理理论可知,一个信号进行FFT后再进行IFFT的结果应该是信号本身,所以将B(ω)再进行IFFT计算后得到的结果b(t)存入RAM,由上位机读取并与原始信号a(t)进行比较,可以分析整个卷积系统的处理误差。图6给出了计算FFT结果相对误差的Matlab相关程序。

求出A(ω)的最大值max[A(ω)],分别对B(ω)的实部和虚部计算相对误差,得到如图7所示的相对误差曲线。由图6可知,在FFT过程中,相对误差可以保证在0.5%以内。对FFT所得的结果B(ω)做IFFT得到b(t),分析b(t)与原数据a(t)的误差,得到如图8所示的相对误差曲线。

观察图8可知,经过FFT变换和IFFT变换以后的累积相对误差保持在±3%以内,主要原因是FPGA计算FFT和IFFT过程中由于精度的要求,进行数据舍去,造成误差的产生。这种误差是由硬件客观条件限制的,不可避免,但是±3%的误差精度完全可以满足实际应用。

本系统由于涉及到高速A/D、高速D/A,所以在PCB设计过程中必须考虑电磁兼容EMC(Electro MagneTIc Compatibility)和抗电磁干扰EMI(Electro Magnetic InteRFerence)性和信号的完整性。总体来说,在进行高速PCB设计过程中,不仅要考虑PCB的元器件布局和布线,同时设计中的接地、去耦和旁路同样重要。例如在A/D部分这种混合信号PCB设计中,由于混合了模拟信号与数字信号,只有尽可能减小电流环路的面积才能降低数字信号与模拟信号之间的相互干扰。一个可行的方法是将地平面分割,然后在A/D转换器下面将模拟地和数字地连接在一起。

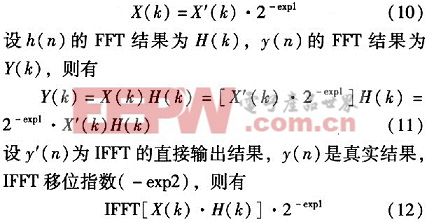

在处理FFT和IFFT核的指数问题时,正常做法是在FFT结束后直接做一次指数调整,在IFFT结束后再做一次指数调整。设经过FFT核后的直接输出结果为X’(k)、对应指数输出为(-expl),x(n)的真实结果为X(k),则有

由式(12)可知,FFT和IFFT的两次指数调整实际可以在IFFT合为一次,可以减少控制的复杂程度。两次调整指数的示意图如图9所示。一次调整指数的示意图如图10所示。

6 结束语

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)