Blackfin处理器及嵌入式mClinux在数据采集系统中的应用

前言

在数据采集系统中,数字处理是系统核心内容之一;然而随着科技发展,越来越多的功能需求使得采集系统的外设也越来越复杂,外设通讯和驱动编写成为一项复杂和繁琐的工作。以应用为中心的嵌入式系统为此类需求提供了一个良好的解决方案,能够适应实际应用中对功能、可靠性、成本、体积、功耗的严格要求。ADI公司的Blackfin系列处理器将嵌入式微控制器和DSP融为一体,取二者之长,提高了系统工作效能,大大降低了成本。同时,多线程的实时嵌入式操作系统也可增强采集系统的实时性、稳定性。对开发者来说, Blackfin处理器和mClinux的结合很有吸引力。

系统结构及硬件平台

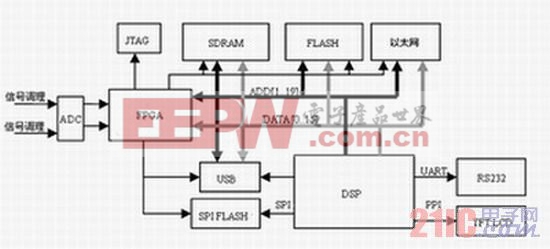

本数据采集系统主要由2个数据采集通道、1个触发通道、ADC转换及存储电路、DSP及FPGA控制部分组成,并包含有以太网、RS232接口、USB、TFT液晶显示部分。系统硬件平台原理框图如图1所示。

信号从采集通道进入,经过信号调理电路进入ADC,被转换后的数字信号即进入FPGA、DSP进行数字控制处理。经过DSP处理过的信号,可送至其它外设以显示、存储,或通讯。

图1 系统硬件原理框图

BF531为系统的核心部分之一,供电电压3.3V,内核电压1.2V,为了使系统能够开机自动从FLASH中启动,设置BMODE为00,即从外部存储器启动。FPGA、片外SDRAM、flash,以及USB和液晶直接和BF531通过地址线、数据线相连。

系统中应用了TFT LCD液晶显示模块FG050605DNC,该LCD控制简单,只有RGB每色5个共15个信号,以及数据使能、数据时钟和行频、场频控制信号。LCD晶直接由DSP控制,DSP的Timer1、Timer2提供行、场频信号,PPI口传输数据,由FPGA提供时钟,配置mClinux开辟一块framebuffer作为显示数据存储区,配合Linux下的液晶驱动,即可工作。

软件设计

由于DSP中运行的是基本上已经成熟的算法和控制流程,所以软件设计的主要工作为在DSP中嵌入操作系统。

U-Boot的移植

U-Boot的移植主要分为两个层面,一个是对CPU的移植,一个是针对Board的移植。U-Boot中已经有大量可直接下载到某些开发板上的程序,为了减小工作量,可选一个最接近自己设计的开发板来进行修改。本设计中采用了stamp目标板。

具体如下:

(1)拷贝board下面的文件夹stamp,重命名为mybf531,作为即将要修改配置的目标板。 拷贝cpu下面的文件夹bf533,重命名为bf531,作为将要修改的cpu bf531。再将board和bf531文件夹中所有关于stamp板的文件名及包含头文件等改为mybf531;将所有关于bf533的文件名及包含头文件等改为bf531。注意文件间的依赖关系,确定是该添加文件还是修改文件,并记录文件改动。

(2)Makefile文件在u-boot根目录下的makefile文件中添加bf531和mybf531的编译规则,如下:

ifeq ($(CPU),bf531)

OBJS += cpu/$(CPU)/start1.o

OBJS += cpu/$(CPU)/interrupt.o

OBJS += cpu/$(CPU)/cache.o

OBJS += cpu/$(CPU)/cplbhdlr.o

OBJS += cpu/$(CPU)/cplbmgr.o

OBJS += cpu/$(CPU)/flush.o

OBJS += cpu/$(CPU)/init_sdram.o

endif

mybf531_config : unconfig

@./mkconfig $(@:_config=) blackfin bf531 mybf531

(3)include/configs/mybf531.h板子的功能配置信息大都在include/configs/mybf531.h中,故拷贝stamp.h并修改其中的启动信息和配置信息。重点修改部分如下:

时钟信息:

#define CONFIG_CLKIN_HZ

11059200

#define CONFIG_VCO_MULT

36

#define CONFIG_SCLK_div

5

FLASH信息:

#define CFG_MAX

FLASH_SECT 67

#define CFG_ENV_ADDR

0x20004000

#define CFG_ENV_SIZE

0x2000

#define CFG_ENV_SECT_SIZE

0x2000

#define CFG_FLASH_ERASE_

TOUT 30000

#define CFG_FLASH_ERASE_

TOUT 30000

SDRAM信息:

#define CONFIG_MEM_SIZE

128

#define CONFIG_MEM_ADD_

WDTH 11

#define CONFIG_MEM_

MT48LC64M4A2FB_7E 1

其它配置信息

#define AMBCTL0VAL

0xBBC3BBC3

#define AMBCTL1VAL

0x99B39983

#define VDSP_ENTRY_ADDR

0xFFA00000

并将板子上不需要的功能的宏定义作相应设置。

(4)Board的移植检查board/mybf531/ 中所有文件,首先将board和cpu的相关stamp.h、stamp.c改为bf531.h和mybf531.c,并检查其文件的设置、包含的头文件和宏定义是否正确。在board/mybf531/config.mk中,找到

TEXT_BASE = 0x03FC0000

PLATFORM_CPPFLAGS += -I$(TOPDIR)

修改其中的TEXT_BASE值为SDRAM的最大地址与CFG_MONITOR_LEN之差。

(5)CPU的移植检查cpu/bf531/ 中所有文件,首先将board和cpu的相关stamp.h、stamp.c改为bf531.h和mybf531.c,并检查其文件的设置、包含的头文件和宏定义是否正确。cpu/bf531/cpu.c文件的修改主要在于配置SDRAM页的

系统 应用 数据采集 mClinux 处理器 嵌入式 Blackfin 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)