一种基于ARM内核SoC的FPGA 验证环境设计方法

引 言

随着片上系统(SoC) 设计的复杂度和性能要求的不断提高, 软硬件协同设计(Hardware/ Software Co2de2sign) 贯穿于SoC 设计的始终。软硬件协同设计是一个以性能和实现成本为尺度的循环优化过程,验证设计是其中必不可少的重要环节。目前大多数公司提供的开发验证系统(开发板) 存在两个弱点:一是开发板的性能、规模难以根据特定的设计需求灵活、自由地调节;二是开发板的功能大多数只能进行软件代码的调试,即使ARM公司提供的开发平台也只能调试部分硬件。这两个弱点均在一定程度上限制了软硬件划分的探索空间,使所设计的SoC 不能获得更佳结构实现的能力。

本文利用现场可编程门阵列(FPGA) 重用性好、现场灵活性好的优势,开发一个能进行详细的行为监测和分析的实时运行验证平台,实现软硬件的紧密和灵活耦合,从而克服上述结构的弱点,以全实时方式运行协同设计所产生的硬件代码和软件代码,构成一个可独立运行、可现场监测的验证平台。这样,不但能够提高SoC 流片成功率,加快SoC 的开发,而且可以降低整个SoC 应用系统的开发成本。

验证平台的设计

系统设计

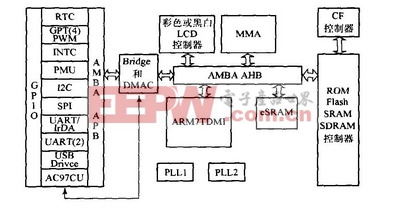

图1 是我们设计的SoC 系统架构, 选用了ARM7TDMI 处理器核, 它是一个RISC 体系的32 位CPU ,具有功耗低、性价比高、代码密度高三大特色(ARM公司本身不生产芯片,普通用户无法获得ARM可综合的CPU 核) ,包括AMBA 总线、DMA 控制器和Bridge 、(外部存储器接口EMI) 、通用串行总线(USB) 客户端控制器、液晶显示器(LCD) 控制器、多媒体加速器(MMA) 、AC97 控制器、通用串口/ 红外(UART/ IrDA) 、通用定时器/ 脉宽调制器(TIMER/ PWM) 、中断控制器( INTC) 、同步外设接口(SPI) 、实时时钟(RTC/ WD) 、时钟和功耗管理单元(PMU) 。

图1 SoC的系统架构

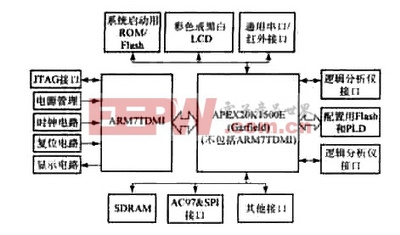

图2 是该SoC 验证平台的结构框图,选用Altera公司的APEX20K1500E 作为验证SoC 用的FPGA ,该器件由一系列的MegaLAB 结构构成,每个结构包含一组逻辑阵列块(LAB) 、一个嵌入式系统块( ESB) 及一个在MegaLAB 结构内提供信号通道的MegaLAB 互连。在MegaLAB 结构和I/ O 引脚间的信号布线通过Fast -Track 互连实现。另外,靠边的LAB 能被I/ O 引脚通过局部互连驱动。

该器件有如下特点:具有多核结构,支持可编程单芯片系统(SOPC) ,密度高,专为低电压应用设计,最多带4 个锁相环的时钟管理电路,多达8路全局时钟信号,每个I/ O 引脚具有独特的三态输出使能控制及可编程压摆率控制[1 ,2 ] 。使用该器件作为AMBA 总线模块、DMA 控制模块、EMI 模块、USB 模块及LCD 控制模块等多个IP 模块的硬件载体, 与ARM7 TDMI处理器构成了一个SoC的验证系统。

图2 中外围电路的主要功能是验证SoC 中各个接口IP 模块能否与ARM7TDMI 核、外部接口单元、硬件驱动软件和实时操作系统协调高效地工作。由于接口(如USB 接口、UART/ IrDA 接口、SPI 和LCD 接口等) 电路结构比较简单,且很多资料都有介绍,在设计时,除了注意通用的设计规则和印制电路板(PCB) 布局布线外,没有特别的要求(总结构框图中所有外围电路都在该开发验证系统中调试成功) ,同时,为了便于分析各个被验证的IP 模块在任意时刻的状态, 我们将APEX20K1500E 的大多数I/ O 引脚都引出到PCB 上,以方便SoC 开发人员使用逻辑分析仪进行信号实时采集和分析,也可让信号发生器产生一些特定信号通过以供系统调试使用。该开发系统在PCB 的设计时还特别注意了电磁干扰的屏蔽。

图2 验证平台结构框图

电路设计

电源的设计

拥有符合FPGA 要求的电压对该验证环境的设计十分重要。根据SoC 的发展趋势和APEX20K1500E增强型I/ O的特点,该平台选用2 . 5V内核电压和3. 3 V 的I/ O 电压,同时提供2. 5 V 和1. 8 V 可选电压,以满足SoC 更低电压、更低功耗的发展要求,方便以后重复使用。

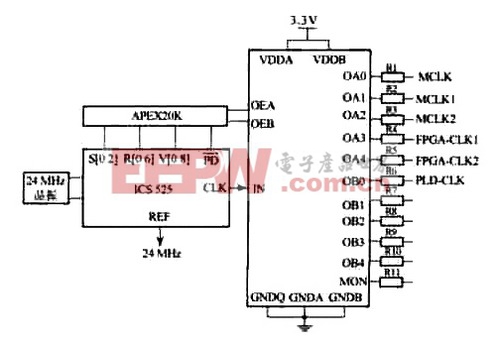

时钟信号电路的设计时钟电路如图3 所示。

ARM7TDMI 核有2 个时钟:存储器时钟MCLK 和内部TCK产生的时钟DCLK。在正常操作期间,内核由MCLK 供给时钟, 内部逻辑保持DCLK 为低。当ARM7TDMI 核处于调试状态(nWAIT 必须为高) 时,内核在TAP 状态机控制下由DCLK供给时钟,且MCLK可以自由运行。所选时钟在信号ECLK上输出,以便外部系统使用。在监控模式下,内核由MCLK供给时钟,且不使用DCLK。所以,首先应供给存储器时钟MCLK。由于该系统除了拥有ARM7TDMI 核外,还包括电源管理模块、复位管理模块、状态和控制寄存器等,应当额外供给时钟MCLK1 和MCLK2。用以验证可复用IP 的芯片APEX20K,也需要提供至少2 个时钟(FP2GA2CLK1 和FPGA2CLK2);用做配置芯片的PLD 也需要提供一个时钟(PLD2CLK) ;各个FPGA 和整个FPGA电路设计都采用全局时钟控制方式,所有的时钟都是由ICS525201 芯片产生,该芯片是一种可调时钟芯片。

图3 时钟电路

时钟频率f CLK用下式调节:

式中:f i 为输入频率;v 为4~511 中的自然数;r 为0~127 中的自然数;OD 值由S[0 ,1 ,2 ]的3 位决定,S2S1S0的组合为:000 对应十进制10 ,001 对应2 ,010 对应8 ,011 对应4 ,100 对应5 ,101 对应7 ,110 对应9 ,111 对应6。注意:时钟电路的频率调节最终通过驱动软件进行各个参数的配置,在FPGA 内应有相应的配置寄存器,同样,下面的复位控制模块也应有复位配置。

复位电路的设计

复位信号包括接口模块中的外部硬件按键复位信号reset 、上电复位信号power on reset 、联合测试访问专家组(JTAG) 复位信号nTRST 和软件调试复位信号nSRST。以上几个信号都是必须的常用复位信号,但ARM7TDMI 核只提供了两个复位信号接口reset 和nTRST ,为此,以上4 个信号必须加入适当的逻辑电路使其最终形成2 个复位信号,复位信号通路必须满足复位时序要求且与时钟信号通路一样越短越好。

JTAG链的设计

通过ARM处理器内的JTAG测试接口,可对整个系统进行探测和配置。使用Altera 公司的QUARTUSII软件对APEX20K器件进行配置时,JTAG链是其中的一条重要配置通路。因此,JTAG链的设计十分重要,其主要设计任务是对FPGA 内的JTAG链与ARM 处理器内的JTAG测试接口进行匹配连接,形成一个统一的JTAG链,它主要包括TCK、RTCK、TDI、TDO 、TMS 和FPGA 配置成功(DONE) ,以及调试请求(DBGRQ) 应答信号(DBGACK) 、系统复位(SRST) 和测试复位(TRST)等信号,其中时钟信号TCK和RTCK通路应当设计得越短越好。至于使用JTAG模式对器件进行编程和配置,可依据参考文献[ 1 ]第5 章进行设计。JTAG数据通路在配置和调试时各不相同,在设计时应当选择几乎无导通电阻的多路选择器对该信号作出合理的分配,对FPGA 器件进行配置和调试时,JTAG数据通路分别如图4、图5 所示。

图4 配置时JTAG数据通路

图5 调试时JTAG数据通路

存储器电路的设计

ARM7TDMI 核虽给出了存储器接口信号,但这些信号对存储器的访问是单一有限、扩展极为不方便的,不能适应不同用户对多种存储器系统( Flash、NANDFlash、SRAM 和SDRAM) 的使用需求,所以大多数SoC都在片内集成了存储器控制器(我们开发的SoC 的片外存储器控制器称为EMI) ,所以该验证平台上设计了以上4 种存储器, 用以验证该EMI IP 核。由于ARM7TDMI 核除了可以实现32 位访问存储器的方式外,也可以支持16 位访存方式,所以,通过在控制线上设置软件可配置的开关实现了3 种数据宽度的访存方式,即8 位(byte) 、16 位(half word) 和32 位(word) 的访存方式。

验证平台的调试和检验

当该系统中的各个模块在PCB 上调试成功后,该验证平台能否很好地验证SoC 的IP 核的开发呢? 我们将已经成熟的AMBA 总线IP 核的Verilog 代码,通过Synplify 综合,利用Altera 公司的QUARTUS Ⅱ软件作布局布线,烧入APEX20K1500E ,再用同样方式将新开发的EMI IP 核的Verilog 代码烧入该FPGA(注意:在该过程中有很多综合和布局布线技巧) ,将其中的SDRAM控制器作为验证示例,选取其中最简单的访问方式,来验证该平台能否使用。该验证平台中使用的SDRAM型号为W981216BH26。上电后,首先要对所有内存区(bank) 预充电,经8 个自刷新周期后需要设置访问模式,即编程模式寄存器。以上3 个过程要求如下:

a) 预充电命令的发出要求:在时钟周期的上升沿处CS、RAS、WE 为低,CAS 为高。

b) 自刷新命令的发出要求:在时钟周期的上升沿处CS、RAS、CAS 和CKE 保持低,WE 为高。

c) 模式寄存器的激活:在时钟的上升沿处RAS、CAS、CS 和WE 为低。

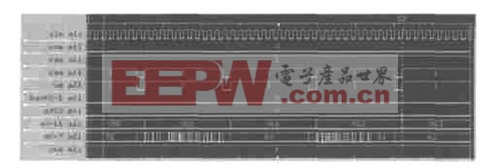

刚开始时,外部端口根本不能出现有用的波形,通过AMBA 总线的一些控制线能够正确地引出,从而排除了该验证平台原理的正确性和PCB 上的硬件可靠性的疑问,再将内部状态机的各个信号采出进行分析后,发现状态机设计得不能工作,经过修改代码后,重新采集端口信号如图6 所示。

图6 预充电、自刷新

从图6 中tr 线处的时序看出,上电后满足预充电命令的要求,紧接着是8 个自刷新命令,最后是模式寄存器的设置,命令字为020H( 00100000B) ,即CASLatency 设置为2 个时钟周期, Addressing Mode 为Sequential 模式, Burst Length 为1 个数据访问模式,模式设置命令通过地址线a02a9 发出,如图7 所示。

图7 模式设置

将该SDRAM的地址映射成为从30000000 的地址空间开始的地址,利用SDRAM驱动程序(协同调试时,应通过实时操作系统进行SDRAM 的读写) , 向以30000000 开始的地址空间连续写入300 个从数据0 递增到299 的数,截取中间一段波形如图8 所示。图6~图8 中各信号如下:clk 为同步时钟,图中是10 MHz ;cse 为EMI 的8 个片选信号之一,即SDRAM的片选信号cs;ras 和cas 为SDRAM 的控制信号;we 为SDRAM 的读写控制信号;bank021 为SDRAM 的4 个bank 选择控制信号;sd10 为既是SDRAM 的控制信号又是地址信号a10;a0211 为不包括a10 的地址信号;dqm021 为字节选择信号;d027 为低位数据线。

图8 写时序

写命令应当满足的时序要求是:在时钟周期的上升沿处RAS 高,WE、CS、CAS 低;第一个要写的数据必须与写命令同时发出。从图8 可以看出,确实能够成功执行写操作访问。注意: 在写之前,必须将该bank激活,只有激活的bank 才能进行读写,图中的激活命令没有显示出来,同时,由于该访问总共300 个地址完全在一个行内,不用对其进行行预充电和再激活(在一个已经激活的bank 内,读写不同的行就要求对该bank进行预充电和再激活) 。

通过图6~图8 ,还可以看出各种操作命令的建立时间Tsetup和保持时间Thold都设置得比较紧,几乎刚好满足。这种IP 核没有给用户留出足够的余量,一旦用户对PCB 的制作稍有不慎,在PCB 板级违反建立时间和保持时间极有可能,造成SDRAM 的不正确访问,所以需要进行检查和修改。经过前端人员的仿真验证,代码中确实存在忽略建立时间和保持时间的问题,修改后重新在该平台进行验证,以上两个时间都能很好地满足,且有足够的余量。另外,从图中可以看出,数据线上有一些毛刺,这是由于FPGA 的I/ O 端口引脚对逻辑分析仪的接口没有很好地分配造成的,重新分配FPGA 的I/ O 端口,绝大部分毛刺都能很好地消除。

通过以上实验,说明该验证平台确实能够达到验证SOC IP 核的目的。要注意的是,当要验证各个IP模块(包括INT 中断控制器、DMA 控制器、LCD 控制器和AC97 控制器等) 之间协同工作时,烧入的代码较多,占用FPGA 资源较多,再加上需要实时运行,例如,播放PM3 实时解码过程中,时钟至少要求60 MHz ,需要工作的IP 核有总线、DMA 控制器、INT 中断控制器、AC97 控制器等,在这种情况下,最好使用Multi PointSynthesis 的综合流程和Timing driven 的综合与优化策略,使用Logic-lock 约束技术和人工干预布局布线,才能达到预期目的。

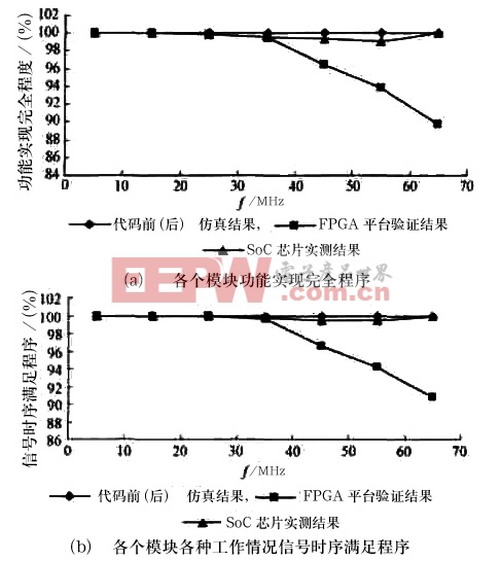

使用该平台对我们开发的SoC 的各个模块进行了验证,并在10 MHz~70 MHz 条件下与代码前(后) 仿真结果和SoC 实测结果进行了比较,结果见图9。可以看出,该FPGA 验证平台在多模块、高速情况下,性能有所下降,需进一步提高综合和布局布线技术。

图9 代码仿真、FPG平台验证及SoC芯片实测结果比较

结束语

本文提出了一种常用的基于ARM内核SoC 的FPGA 验证环境的设计方法,并给出了电路结构框图和相应的外围电路设计。根据该设计, 在FPGA 内实现AMBA 总线、存储器接口和中断控制器,加上外面的ARM处理器核,构成了ARM SoC 的最小系统,根据具体目标系统的需要,可以增加LCD 控制器、AC97 控制器、USB 控制器等模块,构成一个非常实用的验证平台。在IP 核烧入后,可以使用ARM ADS(ARM Developer Suite) 软件开发工具,在线对设计的硬件电路、硬件驱动软件、操作系统和高层应用软件进行调试,从而大大缩短了基于SoC 芯片的应用系统的开发时间。随着FPGA 的飞速发展,用户可以选用更加先进和方便使用的FPGA ,还可选用内嵌ARM 核的FPGA 芯片来构建验证平台。同时,该系统在电压设计、模块选用甚至处理器核的选用方面都考虑了升级扩展技术,可供其他SoC 的验证借鉴。

- 结构化ASIC平台设计要点分析(06-05)

- ARM内核和架构都是什么意思,它们到底是什么关系?(11-22)

- ARM 内核SP,LR,PC寄存器(11-21)

- ARM 内核移植中常见的错误(11-11)

- 决定ARM内核MCU性能和功耗主要因素浅析(11-24)

- 基于ARM内核目标系统中的代码运行时间测试(11-22)