一种基于嵌入式微处理器SIMD核的可重构数据总线设计

摘要:提出了一种基于可重构总线的数据并行体系结构。首先,针对现代多媒体处理中存在的问题,提出了一种基于可重构总线的一维处理单元阵列体系结构;其次,设计各处理单元之间的通信模块以及处理元之间的数据传递方式,即可重构数据总线的设计;最后,通过对几种常用的图像处理算法的验证,表明基于可重构总线的一维SIMD体系结构在逻辑上具有可行性。

前言

由于近些年来消费类设备需求的猛增,如数码相机和数字摄像机等设备,计算机对图像的处理能力近年来成为大家关注的热点。但是,传统的处理器已经不能满足人们对日益增长的处理能力的要求。本文的体系结构正是针对数字图像处理的特点,结合并行处理和可重构技术,提高处理器在图像处理方面的能力。

SIMD计算机是由M.J.Flynn在对计算机系统的分类中提出。根据SIMD结构上的不同,可将其分类为两种。一种是PE-to-Memory结构的SIMD计算机,PE不含局部存储器,而由若干存储器模块通过对准网络与PE相连,各存储模块为各PE共享,所以这种结构又称为共享存储结构的SIMD计算机。另一种是PE-to-PE,即PE由ALU和局部存储器组成,PE间通过互联网络连结,完成PE之间的数据通讯。这种结构也被称为分布式局部存储结构SIMD计算机,在已研究成的SIMD机器中占绝大多数,本文中提出的SIMD核也采用此结构。

基于可重构总线的SIMD体系结构

体系结构模型

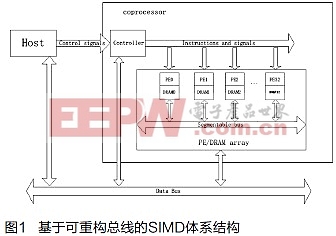

基于可重构总线的SIMD体系结构模型如图1所示,由宿主机(Host)、协处理器(coprocessor)以及数据总线组成。

该模型的存储结构采用哈佛结构,从而在寻址等一系列方面存在优势。由上图可以看出该体系结构的主要部分在于PE阵列,共有32个PE,并且相邻两个PE之间增加了可重构总线,用于负责PE之间的通信,从而引入了邻居本地化,配置总线指令等相关内容,增强了PE之间通信的灵活性。另外,在PE阵列中,该模型还为每个PE设计了DRAM,为每个处理元提供片上内存,减少了与宿主机的I/O次数,从而提高了PE阵列的处理能力。

- 单片DSP处理器功能系统的SOPC技术设计(01-12)

- 数字信号处理器TMS320F241在变频空调中的应用(04-28)

- 用8位微处理器实现数字低通滤波器设计(05-15)

- 如何构造嵌入式Linux系统(05-23)

- 基于DSP的信号采集处理系统(07-21)

- 基于嵌入式Linux的便携式RFID信息采集与处理系统(07-01)