基于DSP/BIOS的数据采集系统研制

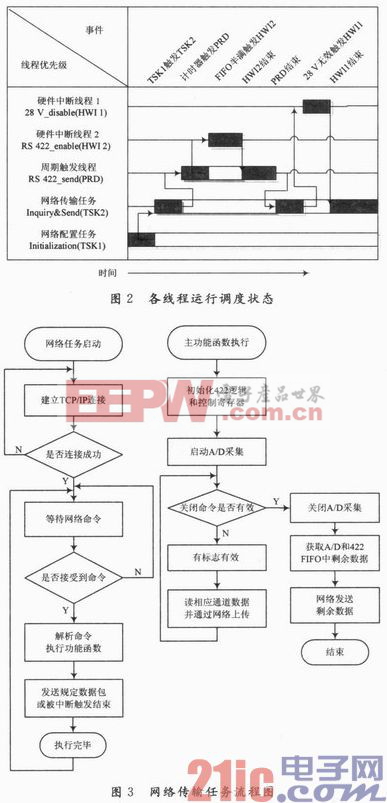

3.2.2 网络任务线程

网络服务启动流程通常是先运行NETCTRL任务线程,完成协议栈的配置、初始化和事件调度,然后开辟新线程执行FTP服务或者HTTP服务。本设计中,网络配置任务线程即NETCTRL任务线程,是DSP/BIOS静态创建的主线程mainTSK,并动态创建网络传输任务线程。网络传输任务是最核心的任务线程,主要完成网络命令解析、通道查询和数据上传的功能,其流程图如图3所示。网络命令分为自检、监测和切断通信下监测3种。自检时不需要被测28 V信号作为AD采集开关,但需要设备本身提供模拟真实信号的以5 ms为周期发送的RS 422信号,采用PRD来实现。通信切断的功能的为了防止设备对原有测试环境的影响。

4 数据可靠性传输机制设计

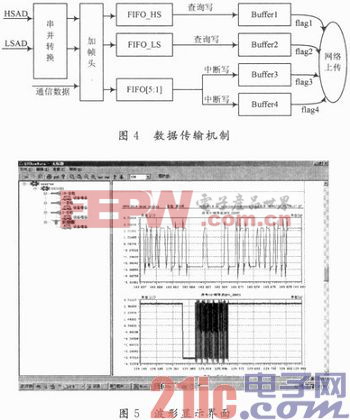

实时采集上传的数据量大,为了保证数据传输的可靠性,要综合考虑网络带宽、AD采样率和缓冲数组等因素。底层数据分为AD采集数据和RS 422通信数据2类,AD采集又分成高速采集和低速采集2个通道。高速采集通道的平均数据量为4 MB/s,低速采集通道的平均数据量为50 KB/s,FPGA中为每个通道配置一个FIFO,DSP通过循环查询判断FIFO标志位,有效即从FIFO读取数据再通过网络上传。RS 422通信数据采用中断方式写到网络发送的缓冲数组中,为了避免由于中断抢占导致的数据冲突,设计2个缓冲数组通过乒乓操作交替写入和上传通信数据。

各环节时间估计如下:通过配置寄存器,DSP访问1次外部存储器需要40个100 MHz的时钟周期。DM642运行TI提供的TCP/IP协议栈,底层通过网络循环发送常数给上位机,经测试,网络平均带宽为80 Mb/s。因此,DSP从FIFO中读取4 KWord(双字节)数据并上传需要的时间至少为2.46 ms,这段时间里4.MB/s采样率下积累的数据量近10 KB。为了防止一个通道数据有效时由于CPU正处理另一个通道的数据而导致第一个通道FIFO溢出的情况,设计每个FIFO的深度为16 KWord,容量达1/4时产生满标志位。数据传输机制如图4所示。

5 结果分析

上位机软件采用VC 6.0结合SQL 2005数据库开发,实现网络控制、数据接收和存储、数据处理和故障诊断以及动态显示信号波形的功能。每一次监测的数据都自动保存到数据库中以便之后的进一步分析和处理。

采样数据波形显示界面如图5所示。

6 结语

本设计利用DSP/BIOS的多任务机制,实现网络控制、数据采集以及网络通信的有效配合,保证底层高速采集的大数据量快速可靠得上传给上位机。同时,以DM642的硬件资源为基础,通过调用NDK提供的APIs,实现了百兆以太网的传输。上位机软件利用数据库作为数据存储平台,可以方便得处理、显示、对比多次采集结果。实际应用表明,该系统稳定可靠、实时性强,在高速实时数据采集领域中有一定的应用价值。

DSP/BIOS DM642 多线程 NDK 数据采集 相关文章:

- 基于DSP/BIOS的数字电视传输流网络采集系统设计(04-12)

- 基于TMS320C6000 DSP及DSP/BIOS系统的Flash引导自启动设计(03-25)

- 基于TMS320DM642的农药喷洒系统(04-22)

- 基于DSP的视频采集驱动程序的实现(07-21)

- DSP并行处理在剖面声纳系统(06-07)

- 基于TMS320DM642的CCD图像采集系统设计(11-14)