浅谈基于C8051F060单片机控制AD9833实现FSK调制

直接数字频率合成技术(DDS)将先进的数字处理技术与方法引入信号合成领域。DDS器件采用高速数字电路和高速D/A转换技术,具备频率转换时间短、频率分辨率高、频率稳定度高、输出信号频率和相位可快速程控切换等优点,可以实现对信号的全数字式调制。

DDS芯片--AD9833的介绍

与传统的频率合成技术相比,DDS技术具有很多优点:频率切换时间短、工作频率范围宽、频率分辨率高、相位变化连续和容易对输出信号实现调制等。DDS主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、低通平滑滤波器等构成。其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号用于DDS中各部件同步工作。DDS的实质是对相位进行可控等间隔的采样。

AD9833是ADI公司生产的一款低功耗,可编程波形发生器,能够产生正弦波、三角波、方波输出。波形发生器广泛应用于各种测量、激励和时域响应领域,AD9833无需外接元件,输出频率和相位都可通过软件编程,易于调节,频率寄存器是28位的,主频时钟为25MHz时,精度为0.1Hz,主频时钟为1MHz时,精度可以达到0.004Hz.可以通过3个串行接口将数据写入AD9833,这3个串口的最高工作频率可以达到40MHz,易于与DSP和各种主流微控制器兼容。AD9833的工作电压范围为2.3V-5.5V.AD9833还具有休眠功能,可使没被使用的部分休眠,减少该部分的电流损耗,例如,若利用AD9833输出作为时钟源,就可以让DAC休眠,以减小功耗,该电路采用10引脚MSOP型表面贴片封装,体积很小。

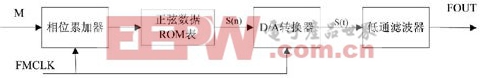

AD9833的内部电路包括数字器件和模拟器件两部分。主要由相位累加器(由加法器和相位寄存器组成)、ROM波形查询表、数模转换器DAC和低通滤波器LPF构成。AD9833的基本结构原理如图1所示。其中M为频率控制字、FMCLK为时钟频率,相位累加器在时钟FMCLK的控制下以步长M作累加,相位寄存器的输出与相位控制字相加后输入到正弦查询表地址中。正弦查询表包含1个周期正弦波的数字幅度信息,每个地址对应正弦波中0°~360°范围内的1个相位点。查询表把输入的地址相位信息映射成正弦波幅度的数字量信号S(n),经D/A转化器变成阶梯波S(t),再经低通滤波器平滑后就可得到合成的信号波形。其形状取决于波形ROM中存放的幅码,因此用DDS可以产生任意波形。输出正弦波频率为:fOUT=M(fMCK/228),其中,M为频率控制字,由外部编程给定,其范围为0≤M≤228-1 .

图1 AD9833的基本结构原理图

硬件电路连接

本设计用Silicon Labs公司推出的完全集成的混合信号片上系统C8051F060来控制AD9833,C8051F060有大量的数字资源需要通过4个低端I/O端口P0、P1、P2和P3才能使用。P0、P1、P2和P3的每个引脚既可定义为通用的端口I/O引脚,又可以分配给一个数字外设或功能(例如:UART0或INT1)。不管引脚被分配给一个数字外设或是作为通用I/O,总是可以通过读相应的数据寄存器得到端口I/O引脚的状态。

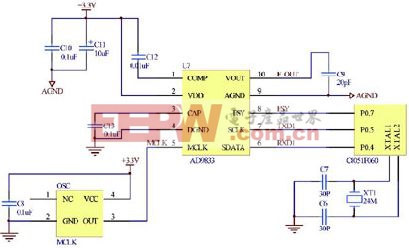

AD9833与单片机C8051F060连接时,使用单片机的3个I/O口和AD9833连接。FSYNC(控制输入,低电平有效)与单片机的可编程管脚P0.7连接,SCLK(串行时钟输入)与可编程管脚P0.4连接,SDATA(串行数据输入)与可编程管脚P0.5连接。三个可编程管脚都可用软件编程实现数据的传送。硬件电路连接如图2所示,单片机产生控制信号和波形参数,通过串行接口将数据传送到AD9833,经AD9833输出的正弦波信号再经低通滤波后输出。

图2 硬件电路连接

软件控制

写数据到控制寄存器

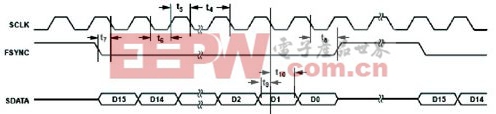

单片机传送数据到AD9833的时序如图3所示:FSYNC引脚是使能引脚,电平触发方式,低电平有效。进行串行数据传输时,FSYNC 引脚必须置低,这种情况下,16个SCLK的下降沿数据被送到AD9833的输入移位寄存器。在第16个SCLK的下降沿FSYNC可以被置高,当然,也可以连续加载多个16位数据,仅在最后一个数据的第16个SCLK的下降沿时将FSYNC置高。需要注意的是,在FSYNC开始变为低前(即将开始写数据时)),SCLK必须为高电平。

图3 串行时序

单片机写16位数据到AD9833时,高位在前,低位在后。用软件

- 基于单片机C8051F060的智能功率柜的设计应用(01-12)

- 关于单片机C8051F060的智能功率柜(09-30)

- C8051F060内置高精度模/数转换器的使用方法(02-29)

- 采用单片机C8051F060的智能功率柜的原理及设计(10-09)

- C8051F060设计的超声波导盲系统(09-29)

- 基于C8051F060和AD9834的频率响应测试仪设计(03-25)