基于S3C2410A的MDB/ICP协议的实现

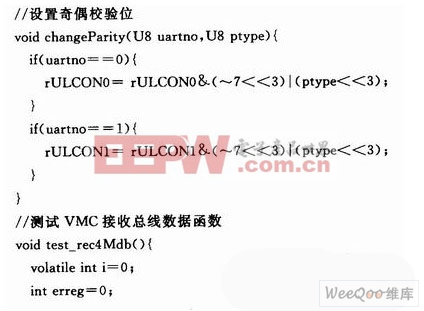

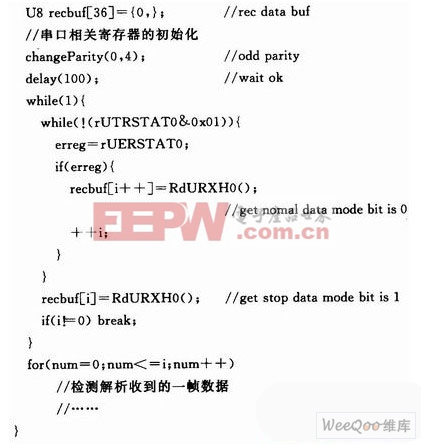

3C2410A接收MDB设备传送的数据是否是结束了。经过分析就可以得到表1所列的推理。 表1 通过上面的分析,开始编写测试程序,结果发现S3C2410A的串口设计的一个bug:当配置UART LINECONTROL REG ULCONn的BITS[5:3]为“101”,选择evenparity接收MDB总线的数据的时候,无论是构造出来的数据1的位数为奇数个还是偶数个搭配具体的模式位,发现S3C2410A的UART ERRORSTATUS REG(UERSTATn)的bit2 frame. error位并不能准确的置位。想想S3C2410A这么流行的芯片竟然还有设计不完美的地方,几乎要放弃的时候,本着一切皆有可能的原则,既然芯片都不可靠了,就索性测试一下,按照表1把ULCONn的BITS[5:3]设置为“100”,选择odd parity接收数据。按常理推断even parity的结果应该和odd parity结果是一样的,抱着试一试的态度,构造测试代码,结果出现了明显的规律:当模式位为“O”的时候,UERSTATn的bit2 frame. error位可以准确的置位;当模式位为“1”的时候,UART TX/RX STATUS REG(UTRSTATn)的bit 0(receive buffer data ready)可以准确置位,正常接收数据。得到这个规律之后,2410 VMC设备就可以准确判断出MDB设备发送过来的数据是否是收到了结束标志。另外,当VMC向MDB设备发送数据的时候,可以按照协议要求当要发送地址字节时可设置ULCONn的BITS[5:3]为“110”,代表parity forced/checked as 1来把奇偶位强制1充当模式位,地址字节发送结束之后调整ULCONn的BITS[5:3]为“111”来发送数据字节。至此,S3C2410A充当MDB VMC设备可以得到完美的解决。下面是VMC接收总线数据的部分调试代码片段。VMC向总线发送数据相对比较简单,有兴趣的读者可以与笔者交流探讨。 结语 本文给出了一种在嵌入式处理器ARM(S3C2410A)上实现MDB/ICP协议的实现方法,在工程实践中,证明该方法准确可靠,满足了市场的需要,拓展了支持该协议的硬件平台,丰富了支持该协议设备的软件功能接口。本文的实现方法也可以应用在其他嵌入式处理器上。 参考文献: [1].S3C2410Adatasheethttp://www.dzsc.com/datasheet/S3C2410A_.html.

- 基于S3C2410A的嵌入式系统的U-Boot移植(01-24)

- MCU_S3C2410之ADC分析(11-11)

- 嵌入式Nucleus PLUS在S3C2410A上移植的实现(11-01)

- 一种基于S3C2410A的液晶屏接口设计(04-13)

- 基于S3C2410A的微型工程地震仪方案设计(03-27)

- 基于S3C2410A的U-Boot移植研究(12-29)