һ������ISA�������1553B�ӿ�ģ������

3.3.3��Ϣ���Ƴ���

����a. readdrv ��ͨ�Ŵ������ֵĻ����������ݣ�

����b. writedrv ��ͨ�Ŵ������ֵĻ�����д���ݣ�

����c. refreshdrv ���ͨ�Ŵ������ֵ����뻺��������ˢ�������

����d. bcreaddrv BCģʽ�¶���Ϣ��

����e. bcwritedrv BCģʽ��д��Ϣ��

����f. mtreaddrv MTģʽ�¶���Ϣ��

4��Ӧ�ó������

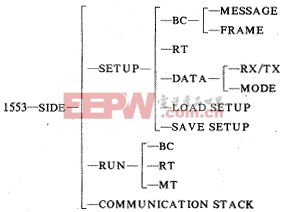

����1553��SIDE�ṩ��һ���˵������Ľ������������е�ѡ����������ݣ��˵�Ϊ���ṹ����ͼ3��

ͼ3���˵���

����ÿ���˵�ҳ�����˵���·�������˵���(�˵��б�)���˵�������״̬�С�״̬����ʾ�˳��˵��ķ�����1553��SIDE����һЩ�쳣�����

�����Ӳ˵������������ַ���֮һѡ���ȼ�����λ�ü��ƶ��������ѡ�

��������û�����IJ���������Ϣ�������ͻ�Ƿ�������ֵ��

4.1����ϸ����

����1553��SIDE�˵����������ֲ���ģʽ����SETUP��RUN��DISPLAY COMMUNICATION STACK��

4.1.1��SETUPģʽ

����SETUPģʽʹ���û��ڲ˵������Ľ�������¶�����������ݡ����е����ÿɱ��洢����ء�

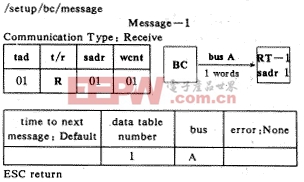

����BC��ʽ֧��127����������Ϣ�����е�ͨ�Ÿ�ʽ��ÿ����Ϣ��ͼ4��ʾ����Ϣҳ������������������Ϣ��Ŀ����Ϣ���͡�RT��ַ���ӵ�ַ���ּ��������ݡ�

ͼ4����Ϣҳ

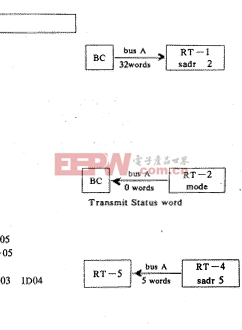

����1553��SIDE��ģ��һ��RT������ȫ����MIL��STD��1553B���ɸ���ϵͳҪ��������RT������ͼ5�ĸ�ʽ��

����

ͼ5��RT���ñ� 4.1.2��RUNģʽ |

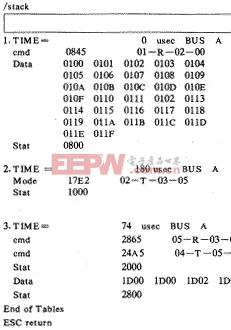

ͼ6��ʵʱ������

4.1.3��DISPLAY COMMUNICATION STACK ģʽ

��������BC��MT�����˵��£�����ʾ����ջ����¼����Ϣ��������Ϣ��š�ʱ�ꡢ�����֡������֡�ͨ�����Լ���Ϣ��ͼ�Σ���ͼ7��ʾ��

ͼ7��ͨ��ջ

5��1553��SIDE���ص�

a. �ɱ��͡��봫ͳ�����ȣ�1553��SIDE��һ����CPU����˫��RAM����EPROM��1553B����װ�ã�

b. ����ISA�������ֱ����������û����������������£�1553��SIDE���ƶ���ISA�����������״̬��

c. ���ϵͳ��1553��SIDE�ṩ����ϵͳ��Ϸ�ʽ��ֱ����Ϸ�ʽ�ͱ�ѹ����Ϸ�ʽ����ϵͳ�����ѡ�ã�

d. 1553��SIDE��DDC��IDEA�����������൱���ƣ�����ʹ�ú�ά����

������

����1553��SIDE���������ơ����������Թ��̣��似��ָ���������Ҫ���ڵͳɱ�����ʹ�á���ά�������������֮������1553B���߲�Ʒ������ϵͳ�������ԡ������һ����װ�á�

�����

1��DDC MIL��STD��1553B designer��s Guide

2��MIL��HDBK��1553B

3��MAX PLUS User Guide

4��DDC BUS��65117��

ISA���� ����� 1553B�ӿ� ������£�

- Linuxϵͳ��ISA����DMA��ʵ��(06-19)

- ����ISA���ߵ�ͨ�ö�DSPĿ��ϵͳ���(05-07)

- ����ISA ���ߵĹ�ҵ����ϵͳ�ӿڵ�·��Ʒ���(12-21)

- PCI����������(12-16)

- ISA���߽ӿڶ���(12-14)

- ISA���ߺ�PCI���ߵıȽ�(12-14)