PIC单片机外部振荡电路设计

晶振设计是单片机应用设计的重要环节之一,因此很有必要了解晶振电路的特点,组成以及如何选用相关电子元件。

PIC单片机有四种振荡方式可供选择,振荡方式经配置寄存器CONFIG的F0SC1,F0SC0位加以选择,并在EPROM编程时写入。

晶体振荡器/陶瓷振荡器:

XT、LP、HS三种方式中,需一晶体或陶瓷谐振器连接到单片机的OSC1/CLKIN和OSC2/CLKOUT引脚上,以建立振荡,如图1所示。电阻RS常用来防止晶振被过分驱动。在晶体振荡下,电阻RF≈10MΩ。对于32KHZ以上的晶体振荡器,当VDD>4.5V时,建议C1=C2≈30PF。(C1:相位调节电容;C2:增益调节电容。)

表1:振荡器类型选择F0SC1F0SC0振荡方式

00低功耗振荡LP(Low Power)

01标准晶体振荡XT(Crystal/Resonator)

10高速晶体振荡HS(High Speed)

11阻容振荡RC(Resistor/Capacitor

常见问题分析

1:如何选择晶体?

对于一个高可靠性的系统设计,晶体的选择非常重要,尤其设计带有睡眠唤醒(往往用低电压以求低功耗)的系统。这是因为低供电电压使提供给晶体的激励功率减少,造成晶体起振很慢或根本就不能起振。这一现象在上电复位时并不特别明显,原因时上电时电路有足够的扰动,很容易建立振荡。在睡眠唤醒时,电路的扰动要比上电时小得多,起振变得很不容易。在振荡回路中,晶体既不能过激励(容易振到高次谐波上)也不能欠激励(不容易起振)。晶体的选择至少必须考虑:谐振频点,负载电容,激励功率,温度特性,长期稳定性。

2:如何判断晶振是否被过分驱动?

电阻RS常用来防止晶振被过分驱动。过分驱动晶振会渐渐损耗减少晶振的接触电镀,这将引起频率的上升。可用一台示波器检测OSC输出脚,如果检测一非常清晰的正弦波,且正弦波的上限值和下限值都符合时钟输入需要,则晶振未被过分驱动;相反,如果正弦波形的波峰,波谷两端被削平,而使波形成为方形,则晶振被过分驱动。这时就需要用电阻RS来防止晶振被过分驱动。判断电阻RS值大小的最简单的方法就是串联一个5k或10k的微调电阻,从0开始慢慢调高,一直到正弦波不再被削平为止。通过此办法就可以找到最接近的电阻RS值。

外部晶体振荡器电路:

PIC芯片可以使用已集成在片内的振荡器,亦可使用由TTL门电路构成的简单振荡器电路。当外接振荡器时,外部振荡信号)仅限于HS。XT。LP)从OSC1端输入,OSC2端开路。

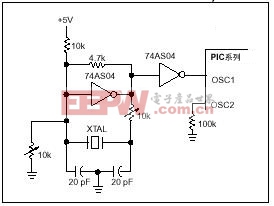

图2所示的是典型的外部并行谐振振荡电路,应用晶体的基频来设计。74AS04反相器以来实现振荡器所需的180°相移,4.7KΩ的电阻用来提供负反馈给反相器,10KΩ的电位器用来提供偏压,从而使反相器74AS04工作在线性范围内。

3:如何选择电容C1,C2?

(1):因为每一种晶振都有各自的特性,所以最好按制造厂商所提供的数值选择外部元器件。(2):在许可范围内,C1,C2值越低越好。C值偏大虽有利于振荡器的稳定,但将会增加起振时间。(3):应使C2值大于C1值,这样可使上电时,加快晶振起振。

图2

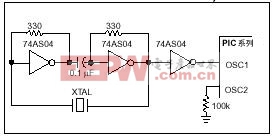

图3

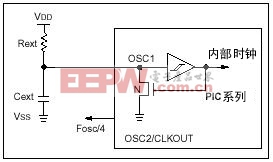

图4

RC振荡:

RC振荡适合于对时间精度要求不高的低成本应用。RC振荡频率随着电源电压VDD,RC值及工作环境温度的变化而变化。同时由于工艺参数的差异,对不同芯片其振荡器频率将不同。另外,当外接电容CEXT值较小时,对振荡器频率的影响更大,当然,我们也应考虑电阻电容本身的容差对振荡器频率的影响。

图4所示的是RC振荡电路,如果REXT低于2.2KΩ,振荡器将处于不稳定工作状态,甚至停振。而REXT大于1M[时,振荡器又易受噪声、湿度、漏电流的干扰。因此,电阻REXT取值最好在3KΩ~100KΩ范围内。在不接外部电容时,振荡器仍可工作,但为了抗干扰及保证稳定性,建议接一20PF以上的电容。

PIC单片机片内有一4分频电路,从OSC1/CLKIN引脚输入或RC振荡器产生的振荡频率fOSC经4分频后从OSC2/CLKOUT引脚输出4分频信号,该信号可用于测试或作为其它逻辑电路的同步信号。

图3所示的是典型的外部串行谐振振荡电路,亦应用晶体的基频来设计。74AS04反相器用来提供振荡器所需的180°相移,330Ω的电阻用来提供负反馈,同时偏置电压.

- 基于PIC单片机的智能型漏电断路器设计(11-25)

- 基于PIC单片机的无线实时监控防盗系统的设计与实现(11-18)

- PIC单片机键盘矩阵扫描C语言程序(12-02)

- PIC单片机控制第一个发光管闪动程序(12-02)

- PIC单片机驱动LCD12864液晶显示闪动字体程序(12-02)

- PIC单片机控制8位流水灯C语言程序(12-02)