Cortex-M3平台上lwIP+AJAX的Web嵌入式应用

摘要:本文基于lwIP以太网协议栈将AJAX动态网页设计技术应用于嵌入式Cortex-M3平台,实现Web嵌入式应用。相比于CGI技术,AJAX实现简易,移植性强,可支持传统IE或是手机等不同的网页访问终端用户。所选Cortex-M3平台内部集成PHY,lwIP协议栈及实时操作系统FreeRTOS均是开源、免费,整个系统成本在60RMB以内,对于成本较敏感的网络互联产品提供了一种解决方案,并给出了硬件原理图及软件代码。

引言

嵌入式系统是融合了SoC半导体技术、电子技术、计算机技术,针对具体应用硬件软件均量身定制的计算机系统。低成本、高可靠性、高灵活性、高集成性使得嵌入式产品在工业领域获得了巨大的发展契机。嵌入式产品一般服务于工业现场,通过RS232、RS485、或是CAN等通信接口与外界互联通信。如今伴随着Internet技术的成熟,带宽的日益提高,公共场所无线网络覆盖,智能手机日益普及,网络化、信息化的要求越来越受到关注,Internet网络互联成为必然的趋势[1]。

目前在实际应用中支持Internet应用的嵌入式系统产品,主要是通过ARM9平台实现,如Samsung S3C2442或是ATMEL AT91SAM9G25平台,操作系统一般是用Linux,网络开发则多是采用传统的CGI(Common Gateway Interface)技术[2]。此种解决方案在成本上过高,仅一颗ARM9处理器就将近70RMB,对于成本敏感的产品无法承担;CGI维护复杂,运行效率低下,每响应一个客户就会打开一个新的进程,当用户访问数量增大时,会严重地损耗系统资源,大幅度地降低系统性能,访问数据库的程序也不容易编写,这也就是最近几年来随着各种新的后台技术的诞生,CGI应用在Internet上越来越少的原因,CGI方式不适合访问量大的应用[3]。

基于此现状,本文给出了一个TI Cortex-M3平台上,运用AJAX(Asynchronous JavaScript and XML)技术实现Web嵌入式应用方案。Cortex-M3平台成本和性能介于ARM9和MCU之间一类处理器,而TI Cortex-M3是目前市场上唯一内部集成PHY,这可进一步降低方案硬件成本。操作系统采用开源的FreeRTOS,相对Linux,FreeRTOS小巧精致,对硬件Flash和RAM需求极小,5KB Flash和0.6KB RAM便可运行,相对于μC/OS-II商业操作系统,FreeRTOS则是完全免费。TCP/IP协议栈采用瑞典开源免费的lwIP(Light Weight IP),一般它只需要0.5KB的RAM和7KB左右的Flash就可以运行[4];网络开发采用AJAX技术,AJAX是一种基于客户端浏览器的语言[5],使用AJAX的最大优点就是能在不刷新整个页面的前提下维护数据。这使得Web应用程序更为迅捷地响应用户交互,并避免了在网络上发送那些没有改变的信息[6]。由于采用了高性价比处理器平台和免费开源的系统软件,整个系统成本可控制在60RMB以内,为成本较敏感的网络互联产品提供了一种解决方案。

系统硬件设计

TI推出的Cortex-M3 LM3S9D96,提供丰富的片内外设:片上集成512KB Flash,96KB RAM,18通道ADC,1个USB(OTG),2通道SPI,2路CAN,3通道UART,1路10/100M Ethernet,内部集成PHY,看门狗,支持EPI、NVIC和DMA,65个通用IO,处理速度80MHz,ROM固化了FreeRTOS操作系统,Bootloader及常用外设操作接口函数库,方便快速高效产品开发。

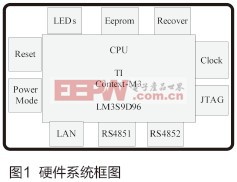

基于LM3S9D96平台的硬件系统框图如图1所示。

?

?(1)PowerMode:系统工作电源,采用DC5V,由外置Adaptor设备提供。整个系统的电源包括:5V,3.3V及5V_ISO(用于RS485通信电源)。

(2)RS4851/RS4852:系统通过RS4851或RS4851接口电路实时采集现场设备运行数据。

(3)LEDs:通过4个LED指示一些重要功能模块的工作状态,如5V电源,RS4851,RS4852及LAN的通信状态等。

(4)LAN:实现标准TCP/IP互联网通信。

(5)Clock:为整个系统提供时钟源。

(6)JTAG:软件开发调试接口。

(7)EEPROM:采用512Kb SPI接口式EEPROM,存储一些采集到的重要运行数据及系统配制参数如IP地址,子网掩码,网关及DNS服务器,Internet时间服务器,时区等。

(8)Recover:恢复出厂设置,当上电时按住此键可使系统所有参数恢复到出厂默认值。

(9)Reset:系统复位电路。

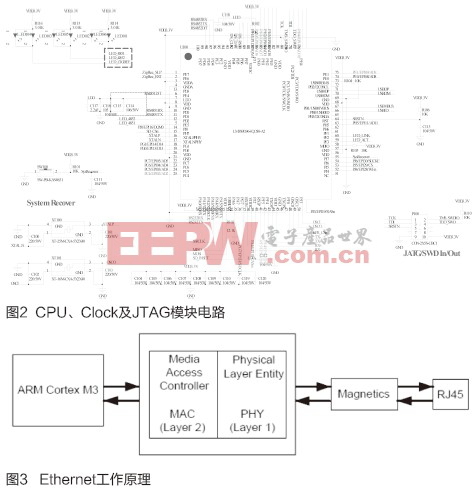

其中CPU、LEDs、Clock及JTAG等主要模块的电路原理图如图2所示。

?

?LAN模块电路,由于TI的Cortex-M3系列片上集成一个以太网控制器PHY和媒体访问控制器MAC,遵循IEE802.3规范,完全支持10BASE-T和100BASE-TX标准。图3是工作原理框图,CPU通过MAC层访问PHY,MAC层提供了以太网帧的发送和接收。MAC层还通过一个内部的媒体独立接口MII给PHY模块提供接口。 ?

所以LAN电路就变得格外的简单,仅需要一个带隔离变压器的RJ45

- 基于CMSIS标准的Cortex-M3的应用软件开发(06-20)

- 基于μC/OS-II和TCP/IP协议的多串口服务器(08-23)

- μC/OS-II就绪表算法在Cortex-M3架构上的适配设计(01-22)

- STM32中断与嵌套NVIC快速入门(01-25)

- 基于STM32的电池管理系统触摸屏设计方案(01-25)

- 发挥ARM Cortex-M3和M4微控制器最大作用的要诀(01-21)