基于FPGA 和USB2.0 的高精度数据采集系统设计

0 引言

随着数字通信技术的逐步发展,高速数据采集系统已经逐步取代传统的数据采集系统,其广泛应用在众多场合。新一代可编程逻辑器件FPGA 都拥有较多的IO 端口以及强大的数据处理能力,这也为高速高精度数据采集系统的研发提供了基础条件。

1 工作原理

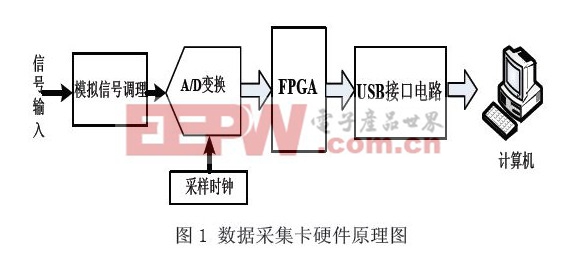

本文设计的数据采集卡硬件原理框图1 如下所示。

如图1 所示,前端模拟电路将外界的模拟信号转化成为ADC能够接收到的数据格式;高速时钟电路提供500MHz 的高速时钟,ADC 在此时钟作用下,进行ADC 变换。在整个数据采集卡中,FPGA 是进行采集控制,以及数据接收的核心。FPGA 按照1 :4 的比率对将接收到的500MHz 的LVDS 差分数据流进行分流和降速。

数据分流之后由于数据速率与USB 接口数据传输速度不同,所以还要进行FIFO 缓冲。FIFO 的写时钟与串行收发器保持同步,当FIFO 缓冲器被写满之后,由FPGA 读取FIFO 缓冲器中的数据,并且将数据通过USB 接口芯片传输到上位机中进行显示或者存储。

2 系统设计

数据采集卡主要包括高速A/D 转换模块、FPGA 主控模块和USB 接口电路三个模块。

2.1 高速A/D 转换模块

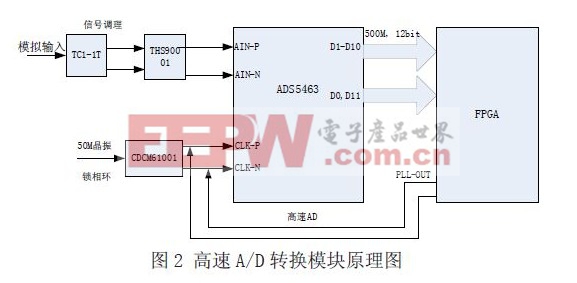

ADC 芯片作为模数转换的核心,设计采用TI 公司推出的ADS5463,其采用流水线型结构,最高采样速度500MSPS,精度12位,拥有高速差分数字接口LVDS.

对于高速ADC 采样电路,模拟信号输入接口的设计不仅要保证足够的传输带宽而且要完成将单端的输入信号变成差分信号的功能。本设计使用射频变压器将单端输入转换为差分输入,并通过TI 公司生产的可级联中频放大器THS9001 芯片实现中频信号放大的功能。

在A/D 转换模块中,采样始终的质量非常重要。在本文的设计中,采用了锁相环芯片CDCM61001 生成采样时钟,并利用FPGA内部PLL 资源倍频生成采样时钟作为备用的采样时钟。本设计是用25M 的时钟倍频20 倍生成500M 以LVPECL 格式的差分电平形式。

高速A/D 转换模块的原理图如图2 所示:

2.2 FPGA 主控模块

FPGA 是整个采集模块的控制核心,其主要的功能是接收数据,并且对数据进行降速、分流以及缓冲,并且将数据传通过USB接口传输给上位机。在本文的设计设计中,选择Cyclone II 系列的EP2C35F672C6,它属于一款中等密度的FPGA,相比较于ASIC低得多的成本在单片机上实现复杂的数字系统。

设计使用FPGA 的Bank3 和Bank4 接收来自ADS5463 输出的高速LVDS 数据,包括DRY(数据输出准备好)以及OVR(数据溢出位)。Bank5 和Bank6 用于USB 接口芯片的控制,其余BANK 留作扩展之用。

在FPGA 主控模块中,AD 输出信号和时钟信号被传输到FPGA 中的DIFFIO_RX p/n 通道上。其中p 表示正差分通道信号,而n 表示负差分通道信号。在这部分的软件设计中,使用altvds模块接收ADC 的输出数字信号、始终信号,并且利用DMUX 对数据流进行串行- 并行转换,以方便对输入信号的后续操作。

数据流在DMUX 模块的仿真结果如图3 所示。

如图3 所示,Data_in 是一路500MHz 的数据流,而dout1,2,3,4 为Data_in 通过DMUX 进行降速和分流之后的结果。从图中可以看出,500MHz 的高速数据流经过DMUX 降速、分流之后的输出较干净、平滑,在高速状态下,达到这种结果是比较理想的,对系统设计上也是很有利的。

- 利用FPGA实现外设通信接口之: 典型实例-USB 2.0接口的设计与实现(06-05)

- 利用FPGA实现外设通信接口之:利用FPGA实现USB 2.0通信接口(06-05)

- 基于总线的嵌入式高速图像通信系统设计(12-21)

- 基于USB 2.0数据采集系统的程序设计(12-21)

- USB2.0接口全接触(12-14)

- 如何轻松地将USB 2.0变为USB Type-C(12-13)