中断处理模式: 外部中断处理和内部中断处理的差异性

相关的中断处理程序。

而在EVIC模式下,外部中断控制器会负责处理周边装置的中断讯号。当周边装置触发中断时,外部中断处理器会负责和周边装置沟通,并将相对应的中断讯号(int_req)和中断需求讯号(evic_ireqval)发给CPU,当CPU接收到中断时,会将中断接收讯号(evic_ireqack)拉起,告知外部中断处理器收到中断,并去处理相关中断处理程序。

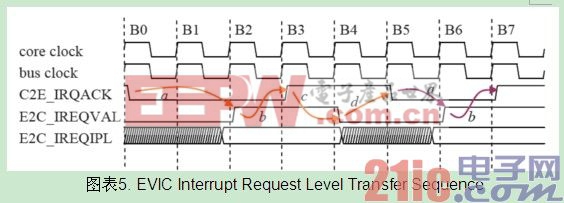

相关处理程序可参考图表 5。在ARC a时,当ireqack讯号为low时,CPU可等待周边装置触发中断。当周边装置触发中断,外部中断控制器将相对应中断讯号int_req和ireqval拉起,告知CPU有中断发生。在ARC b时,当CPU收到中断,则将ireqack讯号拉起,告知外部中断控制器已收到中断。在ARC c时,外部中断控制器将ireqval讯号拉下,并等待CPU将ireqack讯号拉下(在ARC d时),表示CPU可接收新的中断触发。

1.3 System Register Setting

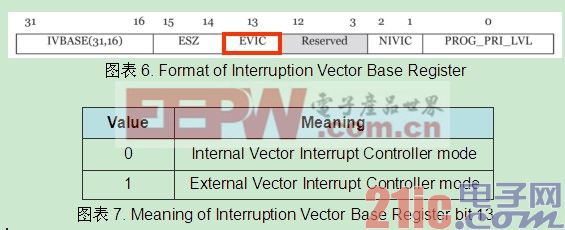

关于上述两种中断模式的选择,用户可透过设定AndesCore™ N968A-S内部的一个system register来达到目的。

该system register为Interruption Vector Base Register(ir3)。其中的第13个bit决定不同的中断模式。其格式如下:

2. Reference Design Architecture

在介绍完中断处理模式相关定义之后,本章节提供在实际整合与应用上的范例,让用户可更了解在不同中断处理模式下的差异。

2.1 主要架构

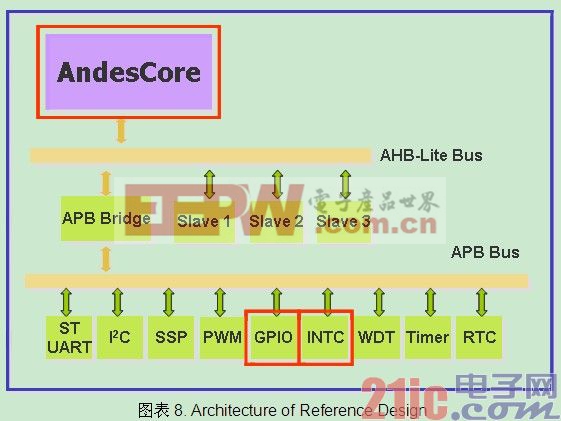

本次所实作的Reference Design主要是架构在Andes mini-platform上,搭配AndesCore™ N968A-S为主要CPU来控制相关周边装置。其主要架构如下图:

将AndesCore™ N968A-S整合在AHB-Lite Bus上,藉由APB Bridge和APB Bus沟通,而相关的周边装置则整合在APB Bus上。在本次范例中,主要会用到GPIO和INTC(中断控制器)这两个周边装置,在不同的中断模式下,利用GPIO来触发中断,再透过INTC与CPU沟通,观察不同中断模式下中断的处理方式。

2.1.1 Design Scenario in IVIC

在IVIC模式下,由GPIO触发中断(gpio_int signal),直接将中断传递给CPU(int_req signal)。当CPU接收到中断时,即可去处理相关的中断处理程序。相关装置之间的整合如下图所示:

2.1.2 Design Scenario in EVIC

在EVIC模式下,由GPIO触发中断(gpio_int signal),INTC收到中断后,会将中断讯号和相关沟通讯号传递给CPU(int_req signal evic_ireqval signal)。当CPU接收到中断时,会将响应讯号拉起(evic_ireqack signal),告知INTC收到该中断,并去处理相关的中断处理程序。相关装置之间的整合如下图所示:

2.2 Example Code

以下将Reference Design中,就本次中断处理模式相关的整合程序部分和测试程序部分,摘要出来说明。

2.2.1 整合程序部分

在系统整合部分,包含AndesCore™ N968A-S和INTC在不同的模式下,整合相关的讯号线,其中透过EVIC_MODE参数来进行不同模式间的切换。

AndesCore™ N968A-S相关RTL片断:

evic_ireqval讯号在EVIC模式下由INTC触发给CPU,在IVIC下可直接给予0值。int_req由INTC或中断来源传递给CPU,告知CPU中断产生。evic_ireqack在EVIC模式下由CPU触发给INTC,告知INTC收到中断。

n9_core n9_core (

...

`ifdef EVIC_MODE

.evic_ireqval (evic_ireqval),

`else

.evic_ireqval (1'b0),

`endif

.int_req (int_req),

.evic_ireqack (evic_ireqack),

...

INTC相关RTL片断:

此中断控制器可透过evic_mode这个输入讯号,来决定该装置是处于IVIC模式或是EVIC模式,因此,在EVIC模式下,给予1值,设定为EVIC模式,在IVIC下,给予0值,设定为IVIC模式。ireqack讯号在EVIC模式下由CPU触发给INTC,告知INTC已收到中断,在IVIC模式下则给予0值。

ncore_intctl intctl (

.PCLK (pclk),

.PRSTn (preset_n~wd_rst),

`ifdef EVIC_MODE

.evic_mode (1'b1),

.ireqack (evic_ireqack),

`else

.evic_mode (1'b0),

.ireqack (1'b0),

`endif

.int_req (int_req),

.ireqval (evic_ireqval),

...

2.2.2 测试程序部分

在测试验证部分,包含AndesCore™ N968A-S在不同中断模式下的设置、INTC相关中断状态的设置和GPIO触发中断的设置。

AndesCore™ N968A-S相关程序片断:

AndesCore™ N968A-S支持两种中断处理模式,透过CPU内部的system register来设置。主要为设置Interruption Vector Base Register,该register的第13个bit用来定义CPU处在何种中断处理模式。在EVIC模式下,需将该bit设置为1,在IVIC模式下,则将该bit设置为0。

!---------------!

!--- Set $IVB ---!

!---------------!

! [31:16] (IVBASE) = 16'$h0

! [15:14] (ESZ) = 2'b00 (4 bytes)

! [1

- LPC2292的伪中断与伪中断处理(03-25)

- Linux 2.4.x内核软中断机制(04-06)

- 嵌入式系统开发之中断控制的实现(04-18)

- uC/OS-II的任务切换机理及中断调度优化(05-11)

- μC/OSII的时钟中断技术研究(06-30)

- 微内核RTOS的核外中断管理(07-27)