基于SDI接口的实时图像增强显示系统

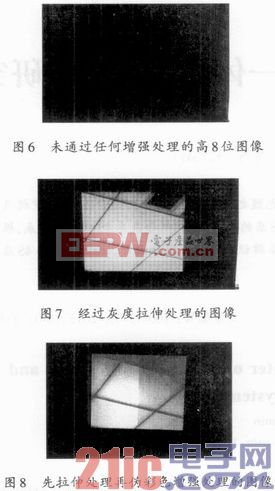

SDI输出显示采用JVC公司专用的SDI监视器,和电路板之间用75 Ω的同轴电缆连接,系统工作后测试了相应功能,并将图像显示在监视器上,图6是显示的未通过任何增强处理的7~14位图像。

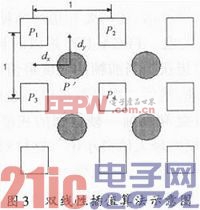

如图3所示,假设原始图像中的某点(x,y),则相邻的右侧和下方像素点位置为(x+1,y),(x,y+1),(x+1,y+1),假设它们的灰度值分别是P1,P2,P3,P4,在水平方向和垂直方向上的位移都是单位1,并假设待插入点的位置坐标为:(x+dx,y+dy)。

那么根据双线性插值算法原理得到插入点的灰度值为:

P’(x+dx,y+dy)=(1-dx)(1-dy)P1+dx(1-dy)P2+dy(1-dx)P3+dxdyP4

化简后得到:

P’(x+dx,y+dy)=P1+(P2-P1)dx+(P3-P1)dy+[(P4-P3)-(P2-P1)]dxdy

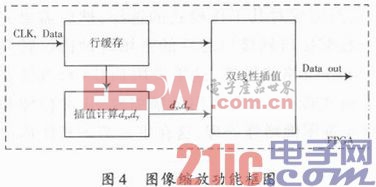

从上式看出,当知道待插值点的偏移距离dx和dy后,那么该插值像素点的灰度值可根据周围的4点得到。该系统中的画幅缩放处理正是采用双线性插值算法,其在FPGA内部实现的具体功能如框图4所示,主要由数据缓存单元、双线性插值单元、插值系数控制单元组成。

在实现图像缩放算法以前,首要算出图像的缩放因子k。这里以一行图像为例,以单位长度“1”表示相邻2个像素的距离,图像缩放前的分辨率为A×1,图像缩放后的分辨率为B×1,则缩放前后的图像的像素缩放因子k=B/A。例如,分辨率为640x512的图像缩放为720x576的图像,则在水平方向上缩放因子k=1.25;垂直方向上的缩放因子k=1.125;根据不同的情况,在水平、垂直方向上的缩放比例因子不同。

根据图4和插值的运算公式,每经过一个像素时钟,插值系数dx,dy需要实时提供给插值运算模块,这就要求FPGA时序同步,并且FPGA各个功能模块能够有效配合。

3 实验结果及分析

将硬件系统和相机连接,该相机基本参数是320x256分辨率,14 b像素深度,帧频25/50可调。通过PC机的RS 232串口连接转一个转换设备,使之满足RS 422差分协议,以便发送命令给硬件系统和返回硬件系统状态。

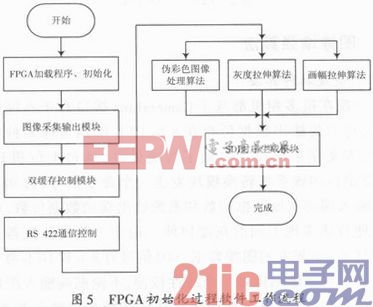

FPGA程序采用模块化方式,分为图像采集输出模块、双缓存控制模块、通信控制模块、伪彩处理模块、灰度拉伸模块、画幅缩放模块和SDI时序生成模块,其中伪彩处理模块、灰度拉伸模块和画幅缩放模块通过RS 422接口发送不同的指令给FPGA,就会触发相应的模块工作,具体FPGA初始化过程中软件工作流程如图5所示。

图7是显示的经过灰度拉伸处理的图像,将14位拉伸成8位。

图8是经过拉伸处理后再经过伪彩色增强处理的图像。图9是经过伪彩色增强处理的拉伸图像再进行画幅拉伸使之全屏显示。

4 结语

本文设计了一种基于SDI接口输出的图像显示系统,在FPGA里面封装了灰度拉伸、伪彩色处理以及画幅拉伸增强算法函数,几种算法可以单独调用,也可以串行一块工作。实验结果表明,该系统可以很稳定地将Camera Link接口或者千兆网口输入图像经协议转换为标清SDI输出,并可以把灰度很低的图像进行对比度增强,极大增强了人眼的视觉效果,由于SDI转换协议以及各个增强算法都在FPGA内部实现,完全可以达到资源优化利用和实时性要求。

- 基于STM32 SDIO接口驱动SD卡的设计(下)(03-07)

- SDIO接口(12-15)

- Linux SDIO总线驱动(12-15)

- 基于ARM含SD控制器的SD卡的SDIO模式驱动解析(12-08)

- SDIO_FATFS_MDK 调试记录(12-03)

- STM32+SDIO+FATFS文件系统 直读SD卡(12-03)