基于AVR单片机的数字滤波器滤除工频干扰的快速算法

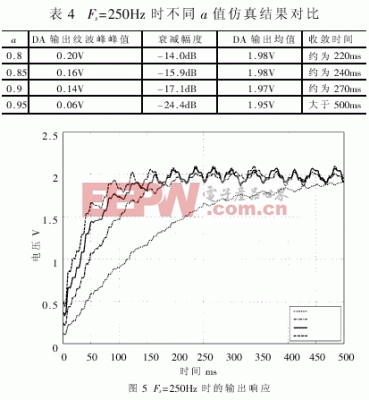

值给y(k-1)所对应的变量即可。因此采用迭代方式进行乘加运算后,整个运算过程只需要两个变量和两个常数参加即可。 通过这种处理,y(k)就可以作为计算下一次输出值y(k+1)的一个已知量,并继续与Q8 数形式的滤波器系数相乘,得到新的输出值。这种处理方式简化了乘加运算的完成过程,节省了系统硬件资源,并降低了处理器开销。 4 采样时间的控制 采用单片机进行数字信号处理,一种有效而准确的数据采集方式就是通过计数器中断服务程序(ISR)控制AD对输入信号进行精确采样。但是(图2)中断服务程序(ISR)的开销影响了AD采样时间间隔的精确度,同时如果中断服务程序(ISR)的开销过大,必然导致AD的最高采样频率的降低。因此,要想获得精确的采样频率,就必须在尽量减少中断服务程序开销的前提下,适当调整计数器中断的时间间隔。这可以通过调整OCRO的预置数来完成。 5 算法流程图 滤波算法是通过中断服务程序(ISR)来完成的,整个应用程序的主函数main()主要负责初始化计数器中断,并处理其它应用。整个程序的流程图如图3 所示。 本算法的C语言代码(附录A)经过AVR-GCC编译器的编译后,“.text”段只有310个字节,大大节省了单片机的flash 空间。 6 基于VMLAB的滤波系统仿真实现 VMLAB的全称为:Visual Micro lab。它针对AVR系列单片机和ST62 系列单片机设计,是一个单片机的虚拟原型框架,可以提供给用户一个真正意义上的虚拟微控制器(MCU)设计实验室。它具有强大的多窗口、多文件的编辑器,微控制器的集成开发环境,拥有一系列的集成开发工具,图形界面的调试器,混合模式的模拟-数字电路仿真器,代码质量检查器等。基于MCU,它可以仿真出包括模拟元器件在内的更多外围设备,并具有交互式器件模拟仿真功能。 假设有用信号是2V大小的直流信号,工频干扰是峰峰值为1V,频率为50Hz的正弦波,建立单片机AD的输入信号表示形式如下: VMLAB 通过工程文件来管理和控制各种仿真信息、硬件连接以及显示I/O 电压波形等。根据本算法的特点,采用Atmega16作为目标单片机,时钟选为8MHz ,建立工程文件。恰当设置OCRO寄存器,使计数器比较匹配中断的时间间隔约为2ms ,这样AD的采样频率近似认为Fs等于500Hz 。经过仿真,对比结果如表3 。 从表3可以看出:随着a的增大,算法收敛的时间变长,同时50Hz对应的衰减幅度增加,衰减的幅度值和理论推导基本一致。另外,当a=0.95时,DA输出的均值变小。这主要是进行循环迭代运算时,需要将16位的变量转化为8位表示形式所导致的。在有用信号失真较小的情况下,为使滤波器达到降低工频干扰的最佳效果,必须恰当选择a 值。经过以上的仿真试验可以发现,当a=0.9 时,衰减幅度、DA输出均值和算法收敛时间表现比较均衡,可以作为一般情况下的选择值。 将VMLAB 中虚拟示波器的显示数据导出到一个*.cvs文件中,用matlab 读出这些数据,并画出不同a值对应的输出响应,如图4 。从图4 可以清晰看出不同a值下算法的性能变化的大致走向。 将AD的采样间隔设置为4ms ,对应的采样频率Fs就变为250Hz ,其它条件不变。通过VMLAB 进行仿真,对比结果如表4 、图5。 对比Fs = 500Hz 的情况,随着采样频率Fs降低,50Hz频率的幅度衰减值会逐渐增加。这主要是因为随着采样频率降低,低通滤波器的截至频率fc也随之降低,相应的滤波器在50Hz处的衰减也就越来越低。根据奈奎斯特低通采样定理,当采样频率小于100Hz时,由于信号频谱混叠,滤波器对50Hz信号的滤波效果将会变差。如果只是对缓变信号进行采样,采样频率比100Hz稍大即可。但是随着采样频率的降低,滤波算法的收敛时间也会增加。因此必须在算法的滤波性能和收敛时间上进行折衷考虑。 本文提出的分配系数法设计数字滤波器,算法速度快、代码效率高、滤波效果理想,是一种实用的数字滤波器设计方法,体现了将算法嵌入到具体硬件的思想。另一方面,将定点小数的表示形式进行适当扩展,这个算法还可以用于10位或16位AD转换精度的应用场合。

- 锁相环控制及初始化简析(08-27)

- 基于AVR单片机的串口转FSK的通信模块设计(01-23)

- 基于AVR单片机的服装压力检测系统设计(05-03)

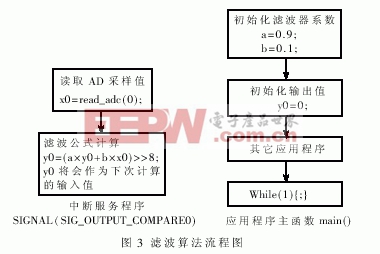

- 基于Atmel AVR单片机的无线图像侦检系统(10-19)

- avr单片机串口多机通讯及实例(12-03)

- AVR单片机入门系列(25)AVR PWM OC0(12-03)