采用ATmega32单片机对FPGA进行配置

Altera公司的ACEX、FLEX等系列的FPGA芯片应用广泛,但其FPGA基于SRAM结构,决定电路逻辑功能的编程数据存储于SRAM中。

由于SRAM的易失性,每次上电时必须重新把编程数据装载到SRAM中,这一过程就是FPGA的配置过程。FPGA的配置分为主动式和被动式。在主动模式下,FPGA上电后主动将配置数据从专用的EPROM(如EPC1,EPC2等)加载到SRAM中。被动模式下,FPGA为从属器件,由相应的控制电路或微处理器控制配置过程,包括通过下载电缆由计算机控制配置和单片机模拟配置时序配置。其中,专用的EPROM价格高,可编程次数少,而计算机配置在现场应用中又很不现实,因此本文提出一种基于AVR单片机的被动配置方式。由于AVR系列单片机的内嵌闪存的容量为8~128kB,可容纳中小规模(10万门以下)FPGA的配置文件并进行配置,另外还可实现多任务配置。以下将以FLEX10K10为例,介绍单片机对FPGA的双任务配置。

ATmega系列单片机

ATMEL公司的ATmega系列单片机根据片内闪存的大小分为ATmega8、ATmega32、ATmega128等。本设计采用的是ATmega32,该单片机片内含16K×16共32KB的片内可编程ROM,可擦写10 000次,能装载2万门以内FPGA的配置数据,最高性能可达16MIPS,可在最短的时间内完成FPGA的配置。如需要配置门数更高的FPGA,可采用MEGA128。

硬件电路设计

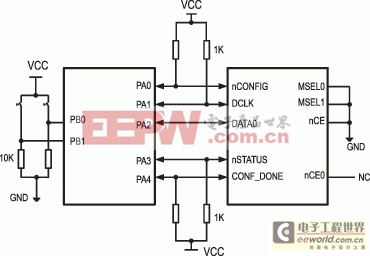

ATmega32内含32KB的闪存,FPGA为FLEX10K10,其配置文件的大小为15KB,因此该方案可实现双任务配置。硬件连接上,采用单片机配置模式时,须将FLEX10K10的MESL0、MESL1、nCE接地,同时将nCONFIG、DCLK、DATA0、nSTATUS、CONF_DONE分别与MEGA32的PA0~PA4相连。MEGA32的I/O口均是可编程的,根据需要将PA0、PA1、PA2设置为输出口,PA3、PA4设置为输入口。另外,需在单片机的PB0、PB1上连接两个按键以选择配置任务。具体电路如图1所示。

图1 硬件原理框图

配置方式

Altera公司FPGA器件的配置方式主要有AS(主动串行方式)、PS(被动串行方式)、PPS(被动并行同步方式)、PPA(被动并行方式)和JTAG(边界扫描方式),使用单片机对FPGA进行配置主要是采用单片机来模拟PS方式的时序,以实现FPGA器件的配置。

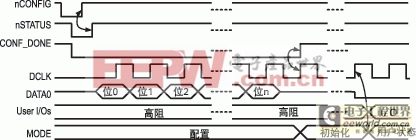

被动串行方式的工作过程如下:配置时需要五个引脚,其中nCONFIG、DCLK、DATA0为单片机的输出引脚,nSTATUS、CONF_DONE为单片机的输入引脚。系统上电后,由单片机使nCONFIG上产生一个大于8μs的负脉冲,FPGA检测到nCONFIG的下降沿后将启动配置过程,nSTATUS和CONF_DONE随之拉低。nCONFIG抬高1μs内,nSTATUS抬高,配置数据从DATA0上由低位到高位依次送出,当所有配置数据全部送出后,CONF_DONE被抬高,当MCU检测到这一变化后即结束配置过程。随后,DCLK必须再提供几个周期的时钟(对于FLEX10K需要10个周期)以供FPGA正确完成初始化,进入用户模式。若配置过程出错,nSTATUS将被拉低,MCU重新启动配置过程。其配置时序如图2所示。

图2 被动串行配置时序图

配置文件

Altera公司的开发工具Quartus II和MAXPlus II可生成多种配置文件,包括sof、pof、hex、rbf、ttf等。该配置方案中采用的是rbf文件,rbf文件为二进制文件,包含了全部配置数据,1字节的rbf数据包含8bit的配置数据,配置时最低位先由低位到高位依次装入。

软件设计

使用单片机对FPGA的设计关键是软件设计。在双任务配置中,两个任务的配置数据分别存放于不同起始地址的连续存储器区域中。单片机上电复位后,进入按键查询状态,检测到按键按下后,单片机从相应起始地址中读出数据并对FPGA进行配置。配置过程按照PS方式的时序要求进行,配置完成后重新进入按键查询状态。控制程序流程图如图3所示。

图3 控制程序流程图

在双任务配置中,两个任务的配置数据分别存放于指定的地址中,由引导程序从指定地址中读出数据并对FPGA进行配置。引导程序和rbf文件(配置数据)的合并是软件设计的关键,以下详述其处理过程。

(1) 将引导程序在ICCAVR下编译并生成mcu.hex,hex文件格式是由Intel公司定义的,是按地址排列的数据信息,数据宽度为字节,所有数据使用16进制数字表示. 以下是一个例子。

:10008000AF5 F67F0602703E0322CFA92007780C361

:1000900089001C6B7EA7CA9200 FE10D2AA00477D81

:0B00A00080FA92006F3600 C3A00076CB

:00000001FF

第一行,“:”符号表明记录的开始。后面的两个字符表明记录的长度,这里是10h。后面的四个字符给出调入的地址,这里是0080h。后面的两个字符表明记录的类型后面则是真正的数据记录, 最后两位是校验和检查,最后一行是结束串,总写成这样;

(2)将fpga1.rbf改为

- ATmega32外部中断嵌套(11-10)

- 基于OPenWrt开源系统的无线视频监控智能车设计(10-29)

- OTG技术在存储测试中的应用(09-07)

- 家用机器人设计方案汇总,包括清扫、保健、灭火等方面(05-11)

- 基于ATmega32的便携式车门压力测试仪设计(04-20)

- 一种基于双MCU的安全光幕设计方案(04-08)