从4004到core i7——处理器的进化史-CPU构成零件-3

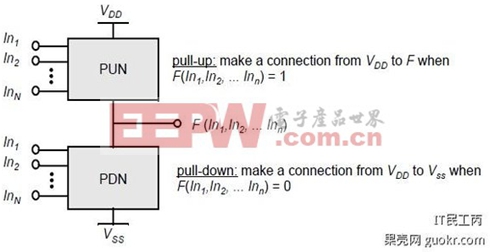

从上面的帖子中我们看到了CMOS工艺下的反相器。如果用一张图总结一下这种设计模式就是下面的这张图

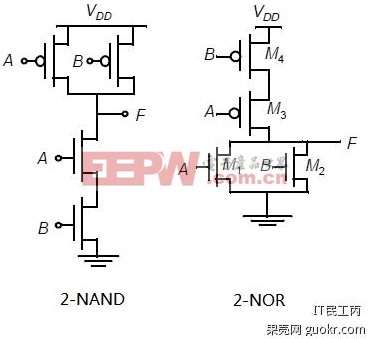

注意,上面的图片中的PUN(pullup network)和PDN(pulldown network)是互补的,也就是说:同一组输入下,要么PUN中存在VDD->输出点的通路,要么PDN中存在输出->地(VSS)的通路,这也正是互补(complementary)的含义。由于不存在由VDD->地的回路,所以CMOS逻辑电路没有静态功耗。我们说CMOS逻辑电路是静态(static)的,即在一组输入下稳定后,输出点是通过一条低阻的(导通的MOS管的电阻大约在10k~100k数量级)通路上拉到VDD或下拉到地的。由于这样的低阻通路是存在的,所以CMOS电路受外界干扰较小,特别受漏电的影响较小(因为电源能向其补充失掉的电荷),这使得CMOS数字电路成为最稳定、最可靠的电路之一。下面我贴两张最常用的逻辑门:2输入NAND和2输入NOR的CMOS实现:

下面的内容是最后的背景知识。

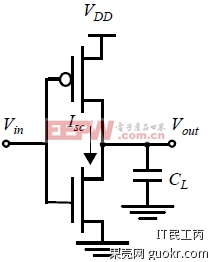

所有以上的分析中我们都在讨论电路的静态特性,即输入稳定相当长的时间后与输出的关系。而在IC的设计中,我们不仅仅关心一个电路功能的正确性(correctness),健壮性(robustness)还关心其性能(performance),即其在单位时间内正确地处理的输入信息量的多少。为此我们不得不引入MOSFET管的一些细节以讨论其动态特性(dynamic behavior),看看下面这张稍显复杂的图。

注意图中的六个电容。这些电容是MOSFET管的寄生参数(parasitic parameter),它们的引入不可避免的,因为相邻的导体之间必然会产生电容。

有了上面这张图做基础,我们再次回到CMOS反相器的例子上。不同的是,这次我们关注的是其中的寄生参数

注意,上面的图中一个反相器在驱动另一个。

显然,在上面的图中,假设Vin突然从0->VDD,那么电容Cgd12,Cdb1,Cdb2,Cw,Cg3,Cg4都要充放电,而充放电的通路就是PMOS管M2。为了简便起见,我们将0.5VDD作为0和1的分界线,并且假设Vin是一个理想的阶跃信号,即从0->1不需要时间。我们发现,从Vin跳变开始,第二个反相器的输入端经过了这么长时间:

0.69R(2Cgd12+Cdb1+Cdb2+Cw+Cg3+Cg4)

才变到0.5VDD,其中R是M2的导通等效电阻。

这个长长的表达式告诉我们:

在动态情况下,CMOS电路的响应时有传输延时(propagation delay)的。输入的信息要等一段时间才能被正确地处理并且得到相应的输出。将多个CMOS逻辑门串连在一起,传输延时便会逐级积累。

一般而言,传输延时大致等于电路工作的最短时钟间隔,即极限频率的倒数。

就一般的深亚微米器件而言,这个时间在10^-11s数量级左右,即频率最高至100GHz左右。

上面的图片简化一下,便得到了下面这张图片:

这个电路绝不仅仅只是一个简单的例子,它告诉我们:

电路的性能取决于MOS管导通电阻与MOS管寄生电容。

这个事实是评价一切电路性能的基础。

举个例子来说,由于有以下关系:

又寄生电容在电压的小范围变化下基本不变,所以CPU在提升频率的同时一般要提升供电电压,以减小0.69RC提高极限频率。

- DSP内嵌PLL中的CMOS压控环形振荡器设计(03-02)

- 基于DSP内嵌PLL中的CMOS压控环形振荡器设计(05-05)

- 宽动态监控摄像机CCD/CMOS-DSP解析 (07-24)

- DSP与单片机通讯方式解析方案 (08-29)

- 基于ATmega162的智能仪器设计(08-18)

- 基于STC单片机的太阳能热水器智能节水控制系统设计(06-02)