从4004到core i7——处理器的进化史-CPU构成零件-2

在上一个帖子当中我们见到了MOS管。下面我们来看一看用它完成的一个最简单的设计。

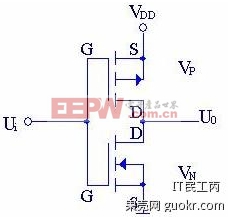

看看上面这个电路。一只PMOS管和一只NMOS管串联起来,共享门极输入和漏极输出。这样的电路,即PMOS在上,NMOS在下被称为互补MOS工艺,Complementary MOS,简称CMOS。在上面的图片中使用的符号,S与D中间的箭头表示的是当这个类型的MOS管导通时底衬中的电子究竟是被吸引在底衬表面还是被排斥出底衬表面。

下面简要的分析一下:

Ui->VDD NMOS 导通 Uo->0 (Pull-down)

Ui->0 PMOS 导通 Uo->VDD (Pull-up)

也就是说,我们仅仅用两只管子就构成了一个可以将输入信号的电平反转的电路。

这个电路叫做反相器。许多经典的教科书在教授数字逻辑时都以它为例,我们也不例外。

进一步分析,我们发现这个反相器具有2个优良的特性。

由于NMOS管的Source接在地上,所以当Ui=VDD时NMOS保证导通,它可以将Uo的电平一直拉到地上;

由于PMOS管的Source接在VDD上,所以当Ui=0是PMOS保证导通,他可以将Uo的电平一直拉到VDD。

更重要的是,只要是NMOS管和PMOS管组合起来就可以保证上面所说的输出电平水平,而PMOS和NMOS的具体参数(比如说,沟道长宽比)不会产生影响。也就是说,我们得到了比例无关的逻辑。这是个非常棒的特性。

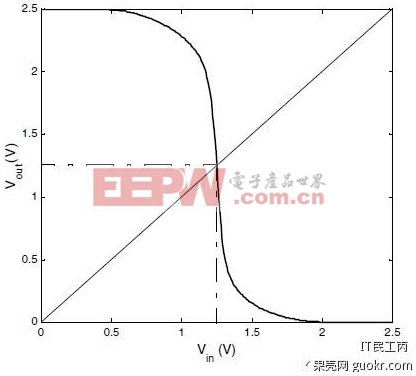

我们再来考虑反相器的电压传输特性。显然,上面关于电平值的分析是不完整的,因为当输入连续变化时输出不可能跳变。看看下面这张图片:

可以看到,CMOS反相器的电压传输特性曲线中间部分非常陡峭。我们把Vout=Vin的点叫做反相器的阈值电压。CMOS反相器的特性是,在阈值电压附近输出迅速完成了电平的切换,而在其他区域输出电平几乎不变。

数字电路的核心思想在于以电平表示逻辑。如果我们定义2~2.5V为‘1’,0~0.5V为‘0’,我们吃惊地发现当在输入为0~1.1V以及1.4V~2.5V时输出电平全都落在我们的定义范围内,全部都是有意义的!也就是说,CMOS具有高噪声容限。如果我们将输入的电平相对于0、VDD这一对“标准逻辑电平”的误差,那么我们发现CMOS反相器可以压缩误差!

比例无关逻辑、高噪声容限、压缩误差,还有后文中提到的静态逻辑,这一切仅仅需要简单地NMOS+PMOS就可以实现,你也许看出为什么现代的集成电路选择CMOS工艺了吧?

- 基于DSP的下一代车载娱乐系统(10-01)

- DSP内嵌PLL中的CMOS压控环形振荡器设计(03-02)

- 基于DSP内嵌PLL中的CMOS压控环形振荡器设计(05-05)

- 宽动态监控摄像机CCD/CMOS-DSP解析 (07-24)

- DSP与单片机通讯方式解析方案 (08-29)

- 如何提升数字控制电源性能?MOSFET驱动器有办法(10-25)