从4004到core i7——处理器的进化史-CPU构成零件-5

前面我说过,要顺带介绍一下除了CMOS之外的逻辑电路。所以下面我们看一看都有哪些选择,以及各自的利弊吧。

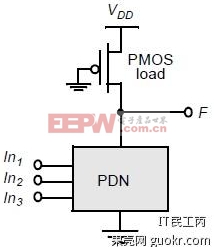

1.伪NMOS逻辑(pseudo NMOS logic)

这种电路中,一个总是导通的PMOS代替了CMOS中的PUN。

Pros:

1.速度快。前面讲过,R与C的乘积决定了IC整体的速度。如果我们干掉PUN自然就减小了C,提高了速度。

2.管子少。一目了然。这个优点在追求面积最小的时候很有用。

Cons:

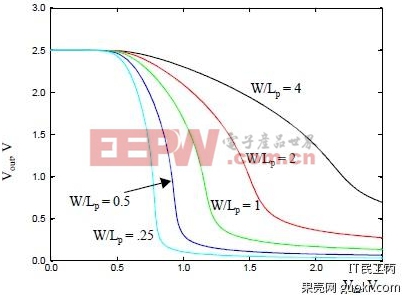

1.电压传输特性不理想,比例相关的逻辑。这里的PMOS的作用就相当于漏极开路输出中的上拉电阻,有它在,输出的下拉就没办法到0了。另外,伪NMOS的电压传输特性曲线见下图,由于PDN中的管子在大部分区域都工作在放大状态所以曲线比较平缓,导致其噪声容限很小。

2.有静态功耗。这就很明显了吧,当PDN接通的时候电流总是需要从PMOS管子上流过。

伪NMOS的最著名的例子就是intel 4004。不过intel可是是迫不得已,因为当时PMOS器件还不成熟呢......

那有没有伪PMOS逻辑呢?答案是一般不这么设计,因为NMOS器件的等效电阻总是比相同参数的PMOS小一些,能提供更好的低电平输出(相对于伪PMOS逻辑的高电平输出)。

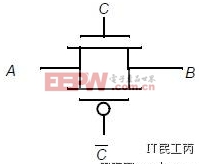

2.传输门逻辑(transmission gate logic)

所谓传输门是指下面接法的一对NMOS和PMOS

这个单元有个神奇的性质:当C=0时,A和B是断开的;当C=1时,A信号能够不损失电平地传播到B!

这种单元在特定的场景下特别有用。例如总线结构中,各个输出端口就通过一个这样的传输门接到总线上,C一般接片选(CS)信号。这样就能够不冲突地通信了!

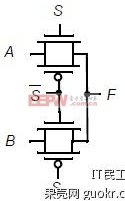

再比如这个2-1数据选择器

3.动态逻辑(dynamic logic)

对,你没有看错,确实存在动态逻辑。

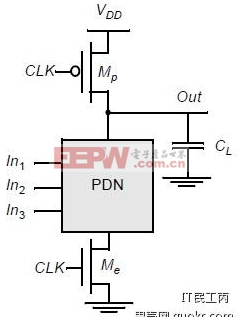

之前我讲的都是静态逻辑。回忆一下,这意味着每个信号都通过低阻回路上拉到VDD或者下拉到地。而在动态逻辑中,信号还可以用存在电容上的电荷导致的电平来表示。我们还是看一张总结这种设计模式的图:

注意,上图中已经出现了时钟(CLK)信号。一个组合逻辑电路中出现时钟很诡异吧。CL并不是专门接的,利用的就是后一级的门级电容!

这个电路的工作分成两个阶段:

第一个阶段,CLK=0,只有上面的PMOS导通。CL被强制冲到高电平。

第二个阶段,CLK=1,只有下面的NMOS和PDN导通。如果PDN中有同路,那么CL就被放电,否则就应该停留在高电平。

不停地重复着两个阶段,就可以使这个电路正常工作!

我们还是来看看这个电路的利与弊吧。

Pros:

1.比例无关的逻辑!由于CLK导致的互补性,这个电路的输出是比例无关的!

2.无静态功耗。很明显,在理想情况下这个电路没有静态通路。

3.快!!!这是动态逻辑最主要的特点,理由和伪NMOS逻辑一样。没有了PUN,输入电容小,自然就快了。

4.晶体管数少。理由同上。

怎么样,动态逻辑很牛吧。不过它的限制也是很明显的。

Cons:

1.易受不理想因素的影响。电容上的电荷常常要受漏电的影响。一个动态逻辑门的输入电容一半在fF(10^-15F)级别,这么小的电容即使是反偏PN结的漏电流也会对它造成重大影响。如果电容上的电容存不住,自然就会产生错误。

2.需要复杂的外电路配合。这主要是CLK信号的生成。

3.难以设计,难以移植。这主要还是1所说的,动态逻辑实在是太不健壮了,在设计的时候要考虑的因素实在太多,以至于至今没有一个可行的非手工的方法。在这块芯片上OK的动态逻辑,可能直接复制到另一块芯片上就出错了。

4.功耗高。这个应该很明显吧,需要不停地给电容充电。

5.需要输入信号的配合。考虑最简单的反相器。如果输入信号有一个1毛刺(也就是说0->1->0)恰好在第二个阶段出现,CL就会被错误地放掉一部分电,后级可能就会错误地判断。动态逻辑常常要求输入的单次、无毛刺的跳变。这通常需要严格的遵守某些规范才能做到。

当然,No pain,no gain。如果不付出一些努力,怎么收获更高的性能呢?动态逻辑常常被用在一些CPU最最核心,最要求速度的地方。比如说,ALU中的加法器。

不瞒大家,intel正是纯手工动态逻辑的行家里手。

再举一个常见的例子,所谓的DRAM(dynamic ram)中的动态就是上面这个意思。只不过它专门接了一只电容(pF级别)罢了。所以DRAM才需要不停地刷新、放大,免得漏电把存储的信息弄错了。大规模的RAM之所以选择动态逻辑,看中的正是它管子少的优点(在DRAM中,一个内存比特只需要用一只NMOS管就可以实现了!)。

到这里,所有的基础知识终于说完了。我们通过下面的两张die photo,感受一下50年里CPU天翻地覆地发展吧~

- DSP内嵌PLL中的CMOS压控环形振荡器设计(03-02)

- 基于DSP内嵌PLL中的CMOS压控环形振荡器设计(05-05)

- 宽动态监控摄像机CCD/CMOS-DSP解析 (07-24)

- DSP与单片机通讯方式解析方案 (08-29)

- 基于ATmega162的智能仪器设计(08-18)

- 基于STC单片机的太阳能热水器智能节水控制系统设计(06-02)