免费的I/O:改进FPGA时钟分配控制

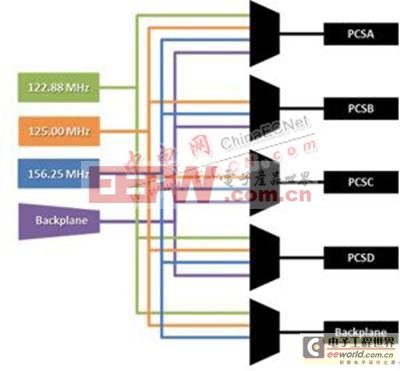

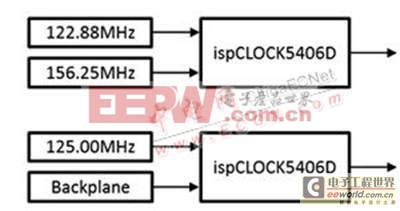

图2 传统AMC时钟网络机制 图3 优化的AMC时钟网络设计 图4 AMC时钟网络控制 可编程性重新定义了时钟网络 综述

利用一个可编程的时钟管理器件,可以大大地优化网络(如图3所示)。该方案仅需要18个I/O来进行时钟分配控制,节省了20个I/O可用于其他功能。此外,使用这种设计节省了超过3平方英寸的电路板面积。

这些方案通过使用两个可编程时钟管理器件来控制(见图4)。有几个板上振荡器可以合成和/或扇出作为几个时钟的输入。所有的时钟变量都可以通过对时钟管理器件的编程来进行管理。

一个可编程的时钟分配IC,如ispClock5406D专门为高性能的通信和计算应用而设计,如PCI Express、ATCA、MicroTCA和AMC。这些可编程IC的主要功能包括一个超低相位噪声的PLL、输出部分支持多种逻辑标准和双偏移控制。

这类可编程时钟分配IC的主要优点包括:

可编程偏移通过减少蜿蜒的走线从而简化了电路板布局,并有助于增加时序容限、缩短设计时间。

能够通过一个可编程的输出阻抗特性来匹配走线阻抗。与更高的输出VCC和接地引脚相结合,提高了时钟信号的完整性。此外,由于输出阻抗可以按每个器件来调整,器件与器件间输出阻抗的差异最小化,从而提高生产合格率。一个片上可编程输出阻抗还可以弥补使用输出阻抗匹配电阻而引起的要用更大的电路板面积的需求。

一个通用扇出缓冲器,可以通过编程来驱动多种信号标准,减少了对独立的(有时部分使用)信号转换器的需求,因此减少了时钟网络的层次,并且降低了整个电路板的时序要求。

低抖动和良好匹配的输出-输出偏移,可以提供额外的时序容限。

每个IC的配置可保存在片上非易失性存储器中,通过JTAG接口进行重新编程。然后器件的某些特定方面可以通过一个I2C接口进行修改。因为该器件的所有的主要功能都是可编程的,设计人员可以使用标准化的器件,如ispClock5406D以满足其系统时钟需求,并且降低成本。

可编程时钟器件集成了主要的时序元件,如一个PLL、分频器、扇出缓冲器、零延迟缓冲器,从而节省电路板面积、降低成本,并提高性能。使用诸如ispClock5400D系列器件,设计人员可以更好地规划其特定系统的理想时钟产生和分配电路,更好地利用其FPGA上的I/O。

时钟分配零延迟缓冲器 I/O需求 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)