零延时隔离技术的RS485总线节点设计

限摆率驱动器,较低摆率降低了不恰当的终端匹配和接头产生的误码。其接收输入具有真正的失效保护功能,当接收器输入为开路、短路、或空闲时,真正的失效保护可使接收器的输出逻辑变高。在上电过程中或接入一个已上电的底板时,其热插拔回路可消除由于对使能和差分接收器输入端的扰动而导致的错误数据。ADuM2483的驱动器具有短路电流限制,并可以通过热关断保护电路将驱动器输出置为高阻状态,防止过度的功率损耗。芯片封装采用易于使用的SOW16封装,工业级温度范围内无需任何分立元件就可实现RS485功能。其主要特点如下:

◆传输速率高,最高可达500 kbps;

◆带载能力强,总线上最多可以挂接256个节点;

◆具有±2 kV的ESD保护功能和热关断保护功能;

◆工业级温度范围为-40~+85℃;

◆瞬态高共模抑制能力,真正防故障装置的接收输入端;

◆低功耗,最大2.5 mA的工作电流;

◆体积更小,集成度高,大大减小了印制电路板的面积。

3 RS485总线节点设计

ADuM2483所隔离的两端有各自的电源和参考地。其中,逻辑端电压为2.7~5.5 V,可以实现低电压供电,从而进一步降低系统功耗;总线端5 V供电,本文设计的接口电路的逻辑端电压采用5 V供电。电源和参考地之间需接入0.1μF龟容,以滤除高频干扰。需要注意的是:图中,GND1与GND2是2个不同的参考地,否则将达不到隔离的效果。

ADuM2483独具的PV(Power-Valid)电源监控功能,可根据供电电源的稳定情况而开断芯片工作。为了避免GND1缓慢上电/掉电 (》100 μs/V)引起的A、B输出抖动情况,ADuM2483设计了PV引脚。当电平低于2.0 V时,此引脚为低,芯片不工作;高于2.3 V时,此引脚为高,芯片正常工作。D1与D2用来防止总线上的瞬变干扰。RS485总线接口电路如图2所示。

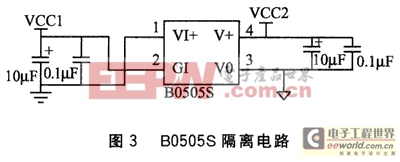

采用金升阳公司的B0505S隔离模块实现收发器两端电源与地完全隔离。其隔离电路如图3所示。

4 RS485总线零延时收发的实现

在RS485总线节点电路设计中,一般要将收发器的接收允许(RE)和发送允许(DE)两个引脚短接,由一根信号线来控制收发的切换。在控制电路中,一般用单片机I/O引脚来控制RS485收发器的收发转换,这样就需要由软件来控制单片机I/O引脚的电平,以达到控制RS485收发转换的目的。RS485 收发器通常处于接收状态,当要发送数据时,由程序控制RE/DE变为高电平,串行通信单元发送数据;等待发送完毕后,程序再将RS485收发器转换到接收状态。发送完毕的标志一般由串行通信的特定寄存器提供状态指示,再由程序去查询。这样造成RS485通信存在以下问题:

◆在想要发送数据和真正能发送数据之间,存在一定的延时;

◆如果发送到接收的转换时机不当,则会造成数据丢失;

◆在接收和发送数据转换期间,容易引入干扰,收到多余的杂乱数据。

在设计RS485总线接口电路时充分考虑到了总线的延时问题,应用一个高速的NPN三极管控制实现RS485总线的零延时收发,如图2所示。

不发送数据时,逻辑端TXD信号为高电平。此时Q1导通,使RE/DE信号线上为低电平,ADuM2483接收允许。发送数据时,若TXD为低电平,Q1 关断,从而使RE/DE信号线上为高电平,发送允许,ADuM2483的输出端A、B上产生表示低电平的差分信号。当TXD为高电平时,Q1导通,使 RE/DE信号线上为低电平,ADuM2483的A、B端处于高阻态。此时靠电阻R1和R2的上拉和下拉作用,使总线上产生正的差分信号,从而将TXD的高电平信号送出。

由以上分析看出,在使用这个电路时,只要程序能保证不同时进行接收和发送的操作,即保证是半双工传送数据,则不必用软件控制RE/DE进行接收和发送的转换,可由硬件本身完成,从而提高了RS485总线接收、发送数据的高速率和高可靠性。

结语

本节点的设计采用新型集成隔离电路的RS485总线收发器ADuM2483,降低了系统的功耗,简化了设计的结构,增强了系统的稳定性。采用硬件的零延时技术提高了节点的收发效率,提高了系统性能。经测试,效果良好,抗干扰能力强,特别适合工业控制场合的应用。

- 零延时RS-485接口电路的设计与应用(09-12)

- 嵌入式系统接口隔离技术及其设计(12-21)

- RS-422/485串行总线隔离技术及应用解决方案(12-21)

- 数模转换器接口隔离技术和外围电路(12-12)

- DSP 与PC 机串行通讯的设计(01-13)

- 基于STM32数据采集器的设计(09-11)