基于SOC的SPI接口设计与验证

ivIDER_LEN,从机选择数目SPI_SS_NB等相关数据。

2.2 spi_slave模块设计

这部分设计作为SPI的从设备与主机进行数据交换,与spi_shift模块时钟同步。通信开始后,从机数据最高位开始串行输入到MISO,主机发出的数据从最低位串行输出到MOSI。

3 SPI接口的功能仿真

本设计采用Verilog HDL编写Testbench,使用ModelSim软件进行功能仿真,并用Debussy软件联合调试并观察波形。为了实现主从设备通信的仿真,编写了一个p_master模块并例化到测试代码里面来模拟主机SoC对spi_master的操作,主要包括一个数据写task、一个数据读task、一个数据比较task。分别测试了1 b,8 b,16 b,32 b,64 b,128 b的数据。仿真全部通过,局部仿真波形如图5所示。

以第一次传输为例进行分析,传输时调用写任务,分别向寄存器divIDER、TX_0、CTRL写入32’h01、32’h5a、32’h308,设定spi_sla ve.data为32’ha5967e5a。由波形看出,数据在ss[0]有效传输,传输完成后MIS0=8’b10100101(即32’ha5),MOSI=8’b01011010(即32’h5a),满足了上升沿发送下降沿接收及高位先开始的数据传输时序。在100 MHz的主时钟频率下,得到串行时钟频率25 MHz,为4分频,符合式(1)的计算。

4 SPI接口的SoC平台验证

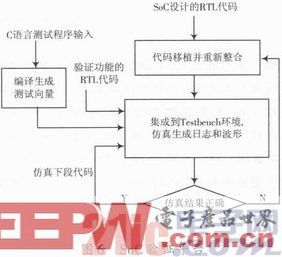

验证用SoC平台具有良好的可重用性和通用性,可以方便的挂接带有AHB/APB总线接口的IP核,并通过内部寄存器对其进行配置和验证,避免了对不同IP设计需要不同的Testbench平台,提高了IP验证的效率。本设计用到的SoC验证平台如图6所示,验证环境为Linux操作系统,仿真工具为VCS。

在SoC验证平台中,SPI接口作为外设连接在APB总线的Slave4端口上,地址空间为0xA400_0000~0XA4FF_FFFF。用C测试程序向Tx0写32’h67,spi_slave.data=32’h0,局部仿真波形如图7所示,MOSI=8’b01100111(即32’h67),MISO=8’b0,结果表明符合要求。

5 结语

本文实现了基于AMBA 2.0总线的、可作为IP核用于SoC设计的SPI接口的设计,并且经过全面的仿真验证,可以看出本设计满足性能要求。

- IP核在SoC设计中的接口技术 (08-06)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- Linux下Sniffer程序的实现(06-12)

- linux操作系统下的进程通信设计(01-24)

- 基于S3C44B0X和uClinux的Socket通信实现(02-28)